Wykład 2:

Sygnały zegarowe

Mariusz Chilmon

m.chilmon@amw.gdynia.pl

uc.vmario.org

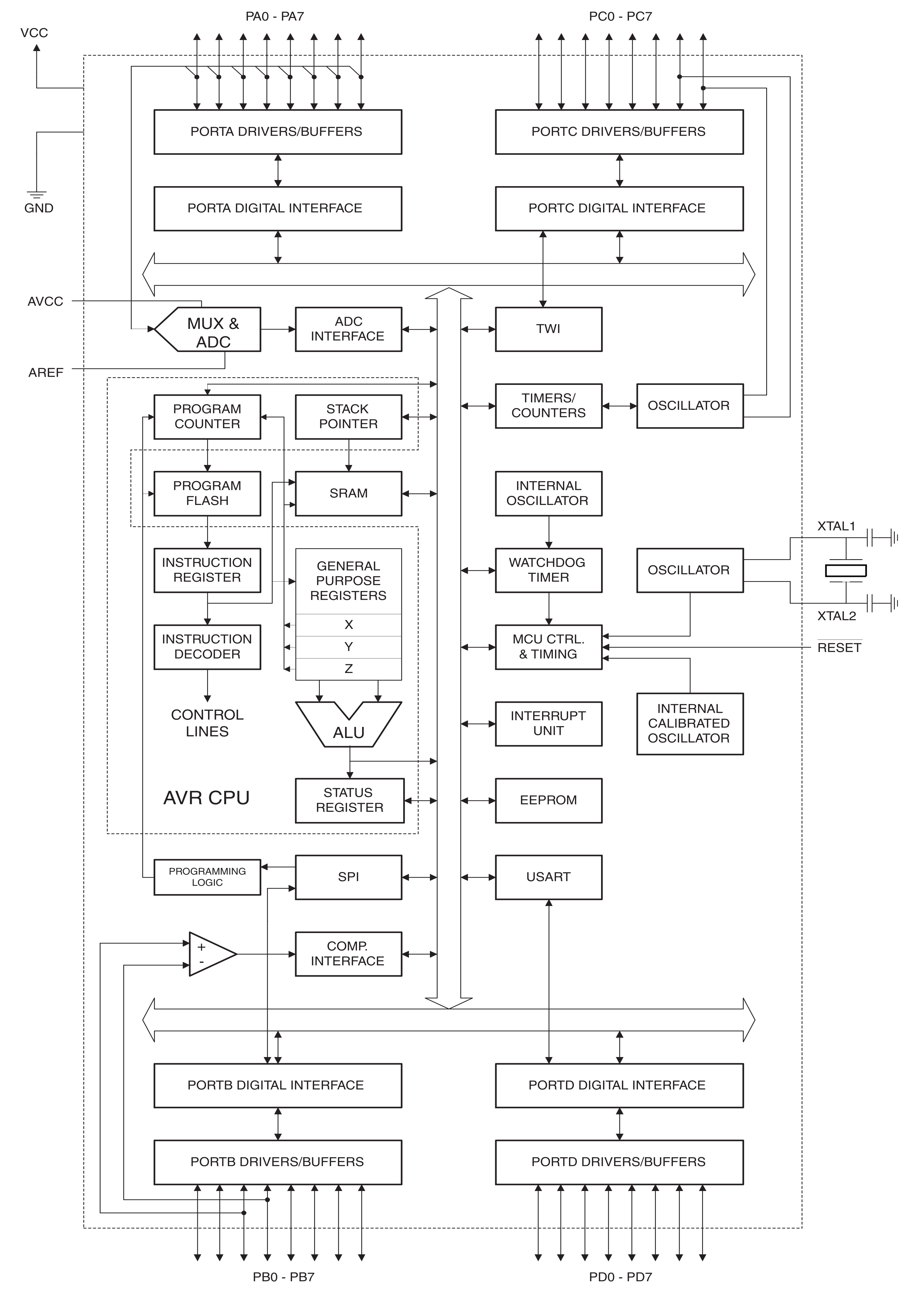

Układy asynchroniczne i synchroniczne

Układy asynchroniczne

Układy asynchroniczne

- szybkie

- energooszczędne

- trudne w projektowaniu

Układy synchroniczne

Układy synchroniczne

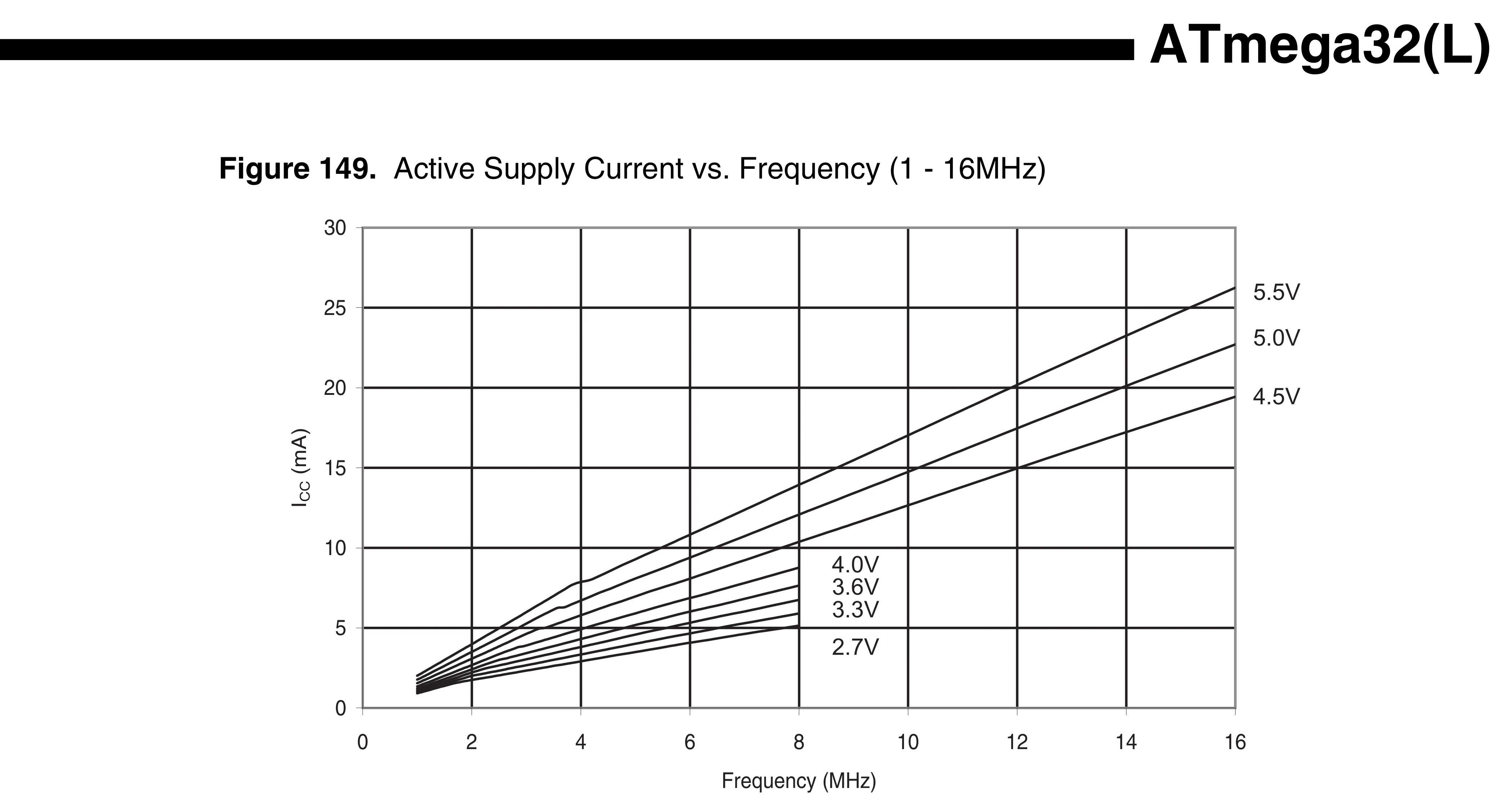

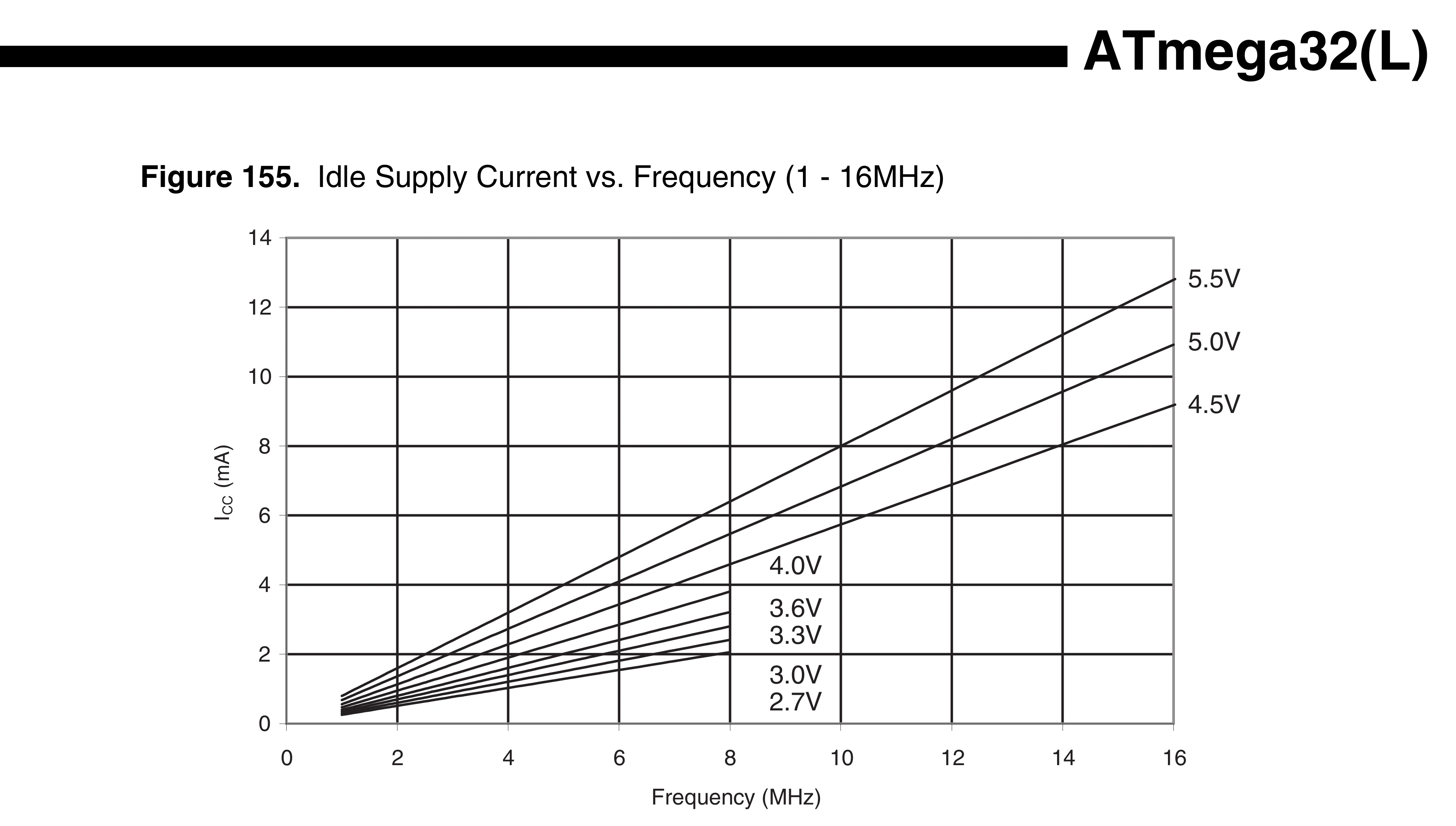

- wolniejsze

- zużywają energię cały czas

- łatwiejsze do zaprojektowania

Pierwszy asynchroniczny mikroprocesor

- California Institute of Technology, Pasadena, 1988–1989

- samoistnie dostosowuje szybkość do temperatury

- samoistnie dostosowuje szybkość do napięcia zasilania

- 4× mniej energii niż synchroniczny odpowiednik przy tej samej wydajności

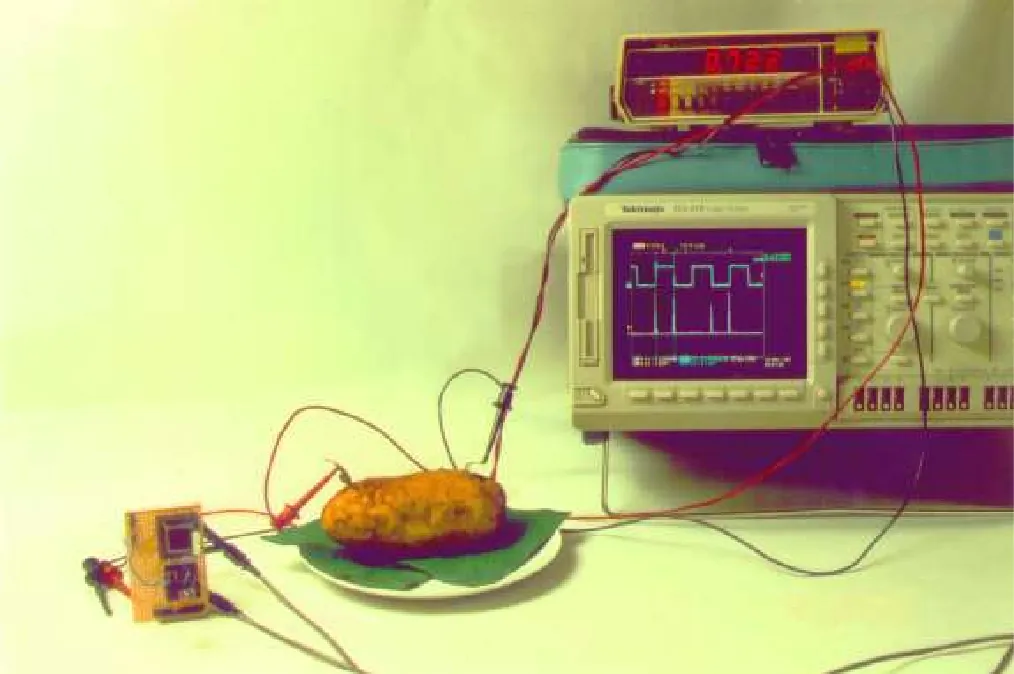

Zasilanie bulwą

Intel RAPPID

- Revolving Asynchronous Pentium® Processor Instruction Decoder

- 1995–1999

- 3× szybszy

- 2× mniejsze zużycie energii

- 5× dłuższy czas projektowania 💵💰🤑

- trudne testowanie

- pewne koncepcje wykorzystane w Pentium 4

Programowanie asynchroniczne ⁕

- nie ma związku z układami asynchronicznymi

- pozwala obsługiwać wiele zdarzeń o stosunkowo długim czasie wykonania bez blokowania programu

Źródła zegarowe

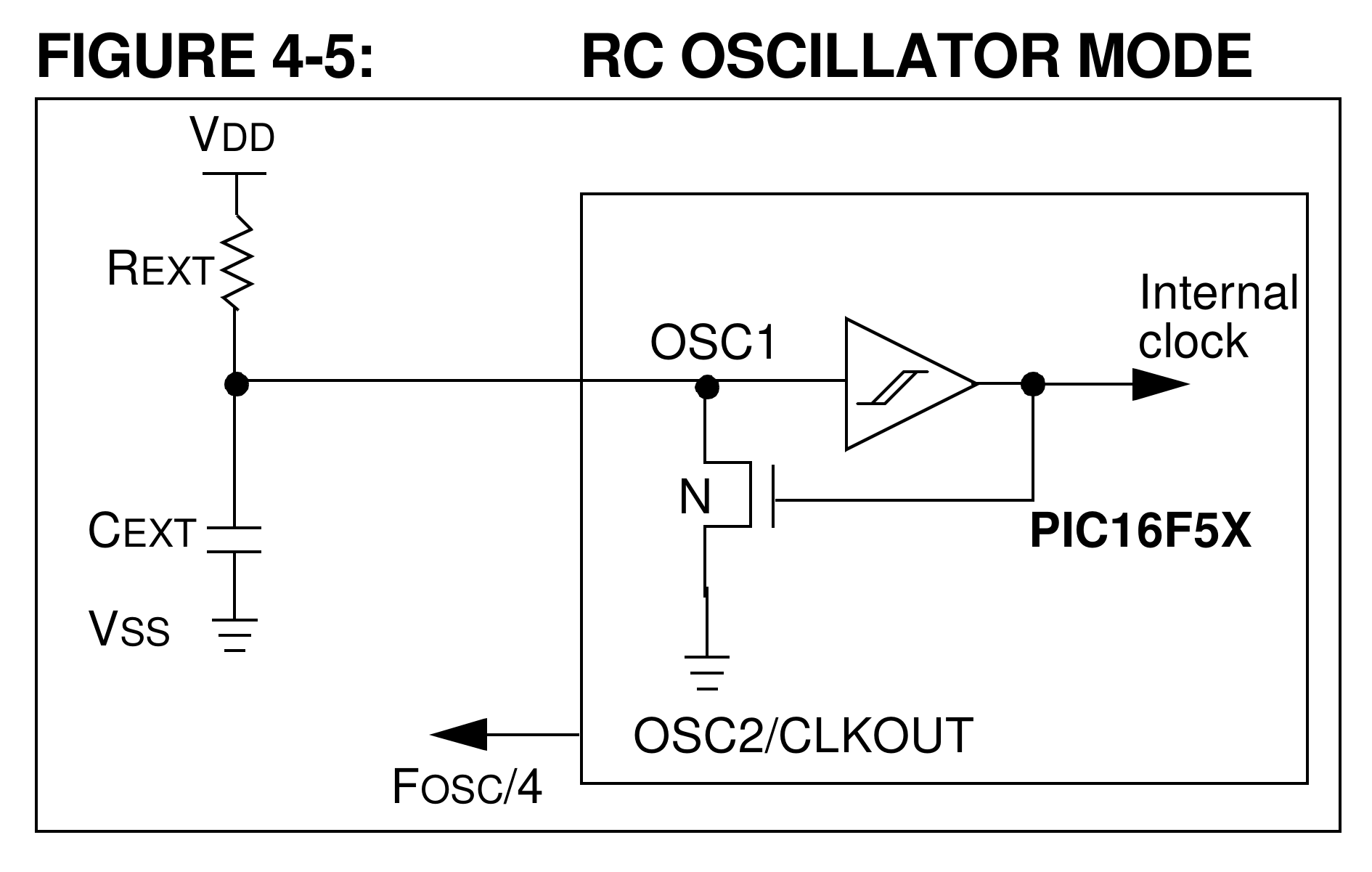

Oscylator RC

Oscylator RC

- tani

- mały (możliwy do wbudowania w układ scalony)

- energooszczędny

- niedokładny

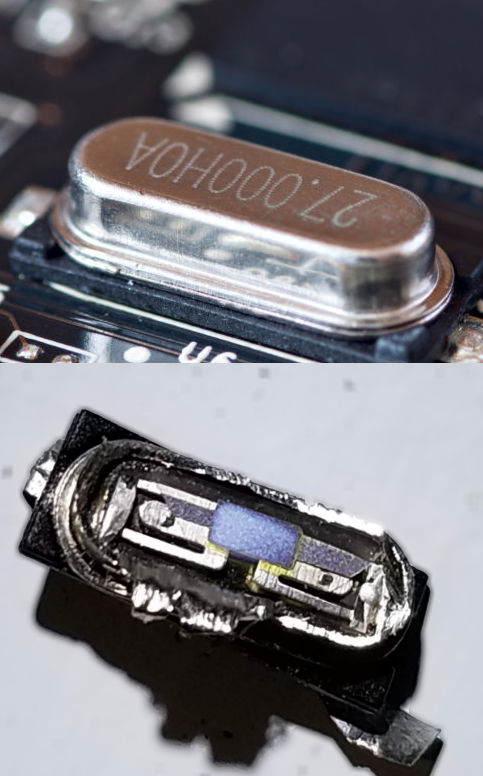

Rezonator kwarcowy (XO/XTAL)

- droższy

- większy

- zużywa więcej energii

- bardzo dokładny (zwłaszcza VCXO, TCXO i OCXO)

Rezonatory kwarcowe

- VCXO

- Voltage-Controlled Crystal Oscillator

- TCXO

- Temperature-Compensated Crystal Oscillator

- OCXO

- Oven-Controlled Crystal Oscillator

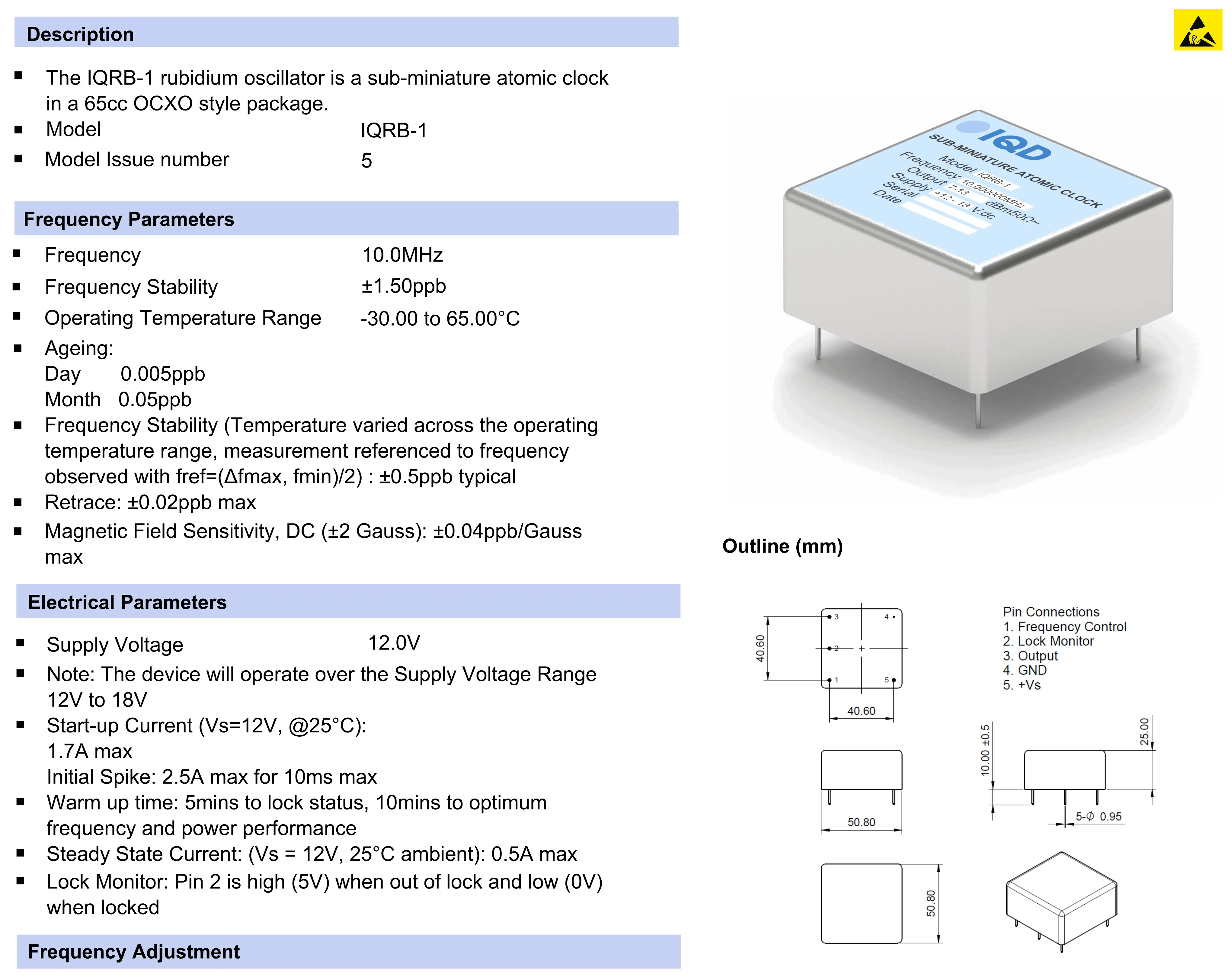

Wzorzec rubidowy

- nieludzko dokładny

- bardzo drogi

- zużywa dużo energii

Odbiornik GNSS (np. GPS) — 1PPS

- bardzo dokładny

- stosunkowo tani

- ma średnie zapotrzebowanie na energię

- dostarcza również czas rzeczywisty

- wymaga sygnału z satelity

Przykładowe dokładności wzorców czasu

| Źródło | Dokładność | Odchyłka |

|---|---|---|

| RC | ±1% | 7h/miesiąc |

| XO | ±20ppm | 51s/miesiąc |

| OCXO | ±100ppb | 3s/rok |

| Rb | ±1,5ppb | 47ms/rok |

Regulacja szybkości zegara

Szybki zegar \(\Rightarrow\) problem

- duże zużycie energii

- wydzielanie ciepła

- wyższe napięcie zasilania

- generowanie zakłóceń

- zjawiska falowe

- czas propagacji

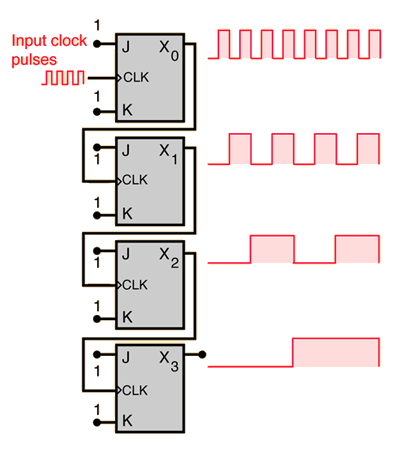

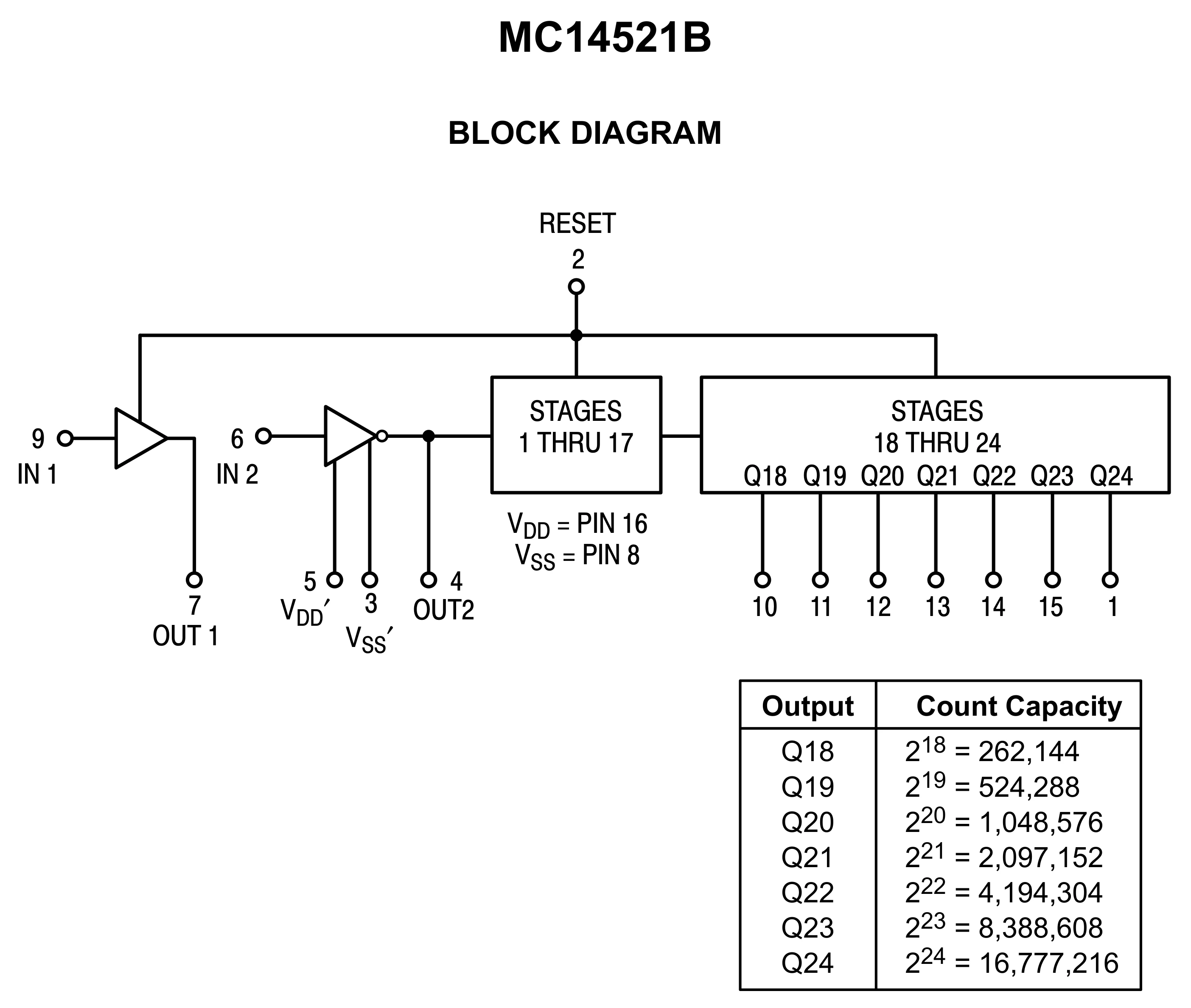

Dzielnik częstotliwości — divider

- najprościej podzielić częstotliwość przez $2^n$

- możliwe jest uzyskanie podziału także przez $n$

- nie ma możliwości zwiększenia częstotliwości

- wymaga zewnętrznego źródła zegara

VCO

VCO — Voltage-Controlled Oscillator

- sterowany napięciem generator RC

- jest źródłem zegara, ale o niskiej dokładności

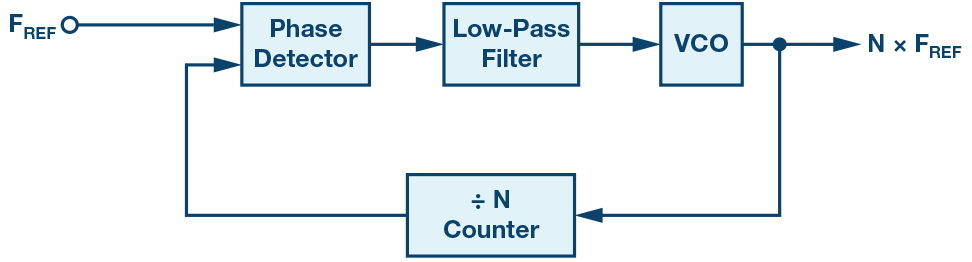

PLL — Phase-Locked Loop

Zalety PLL

- mnoży częstotliwość wzorcową przez $n$

- w połączeniu z dzielnikiem przez $m$ pozwala uzyskać współczynnik $\frac{n}{m}$

- bardzo elastyczne rozwiązanie — must-have dla nowoczesnego mikrokontrolera

Wady PLL

- skomplikowany obwód analogowo-cyfrowy

- często stabilność uzyskuje tylko w pewnym zakresie częstotliwości wejściowej

- uzyskanie stabilności zajmuje pewien czas i może być sygnalizowane w odpowiednim rejestrze

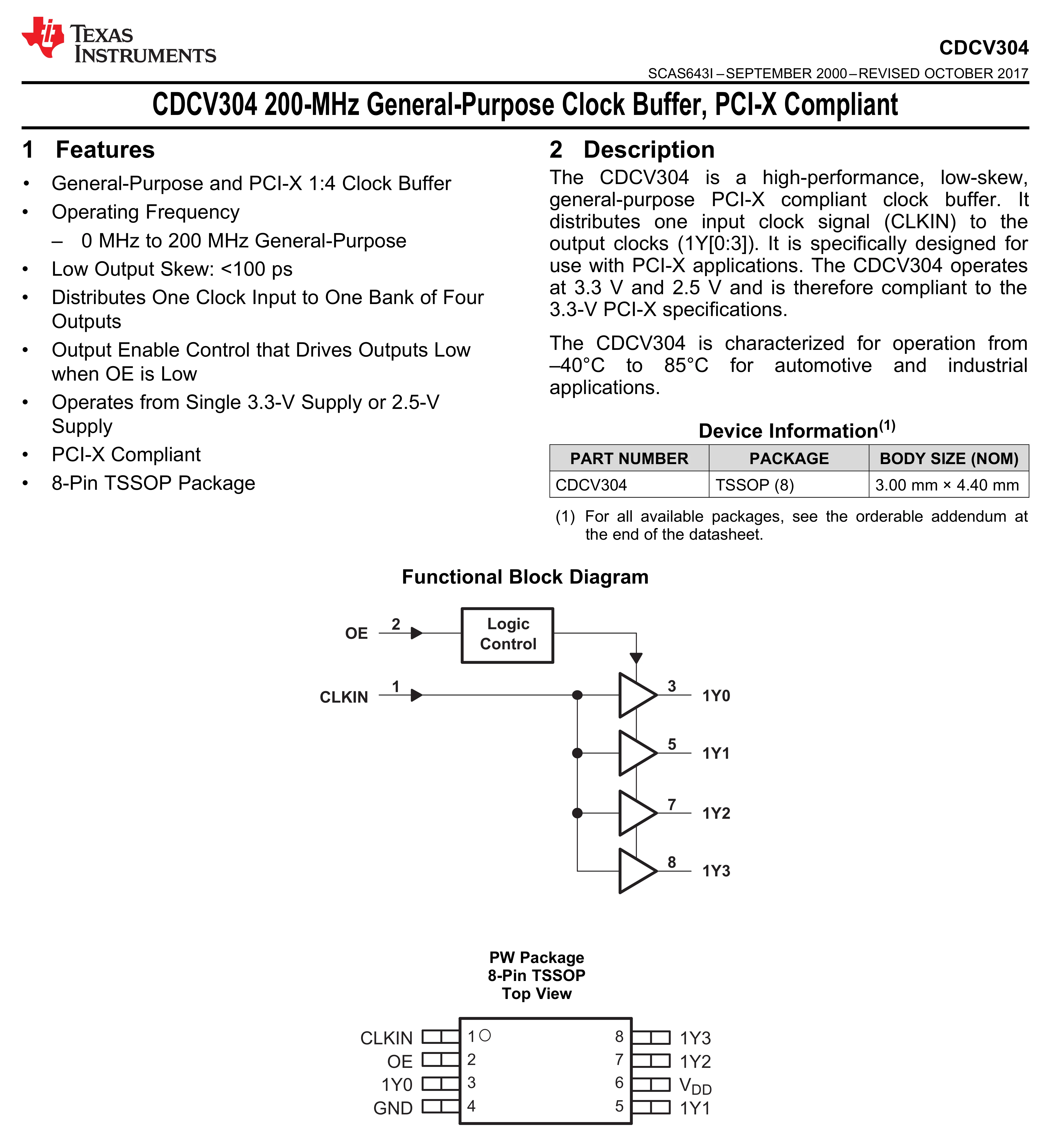

Kondycjonowanie i propagacja sygnału zegarowego

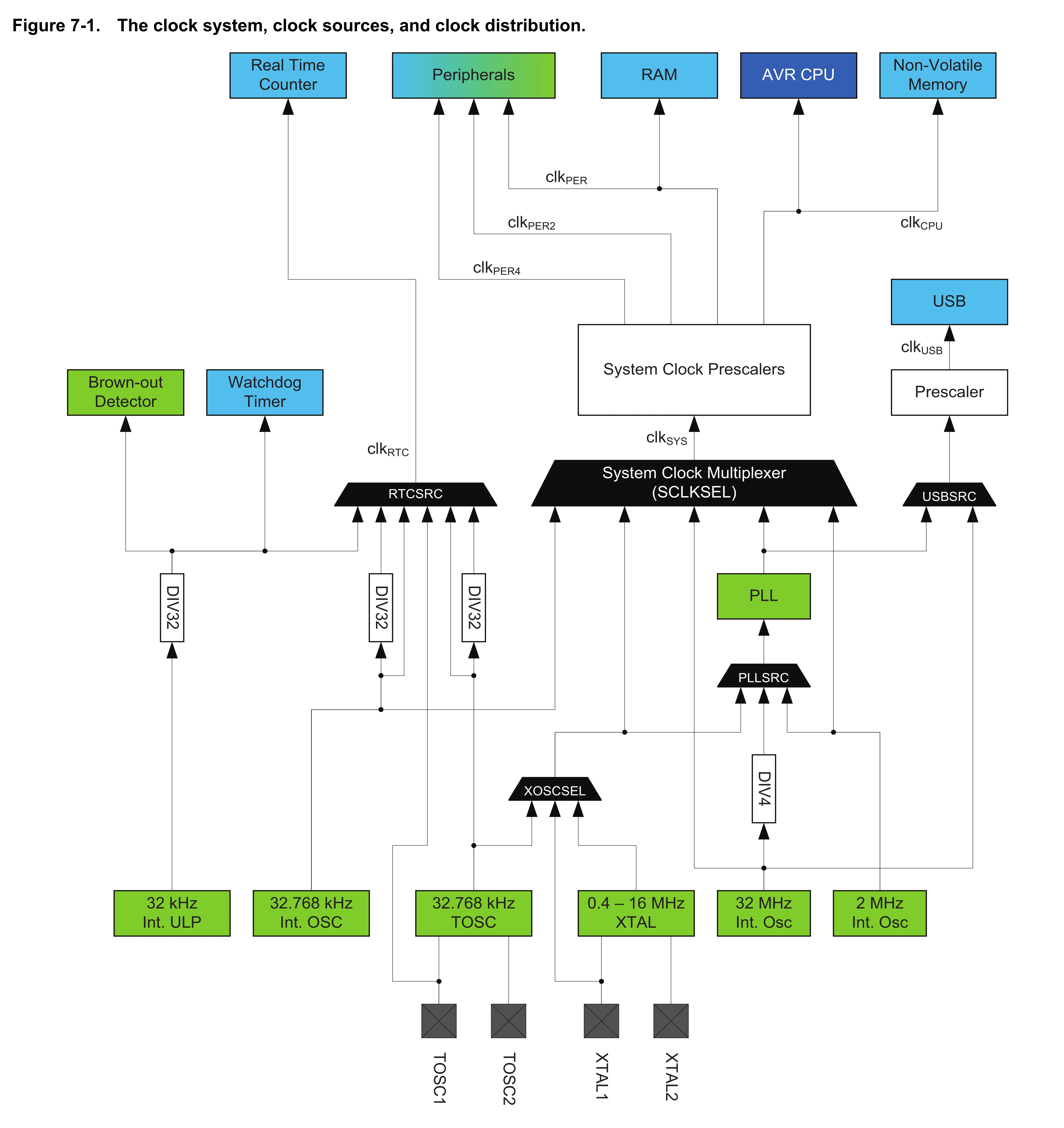

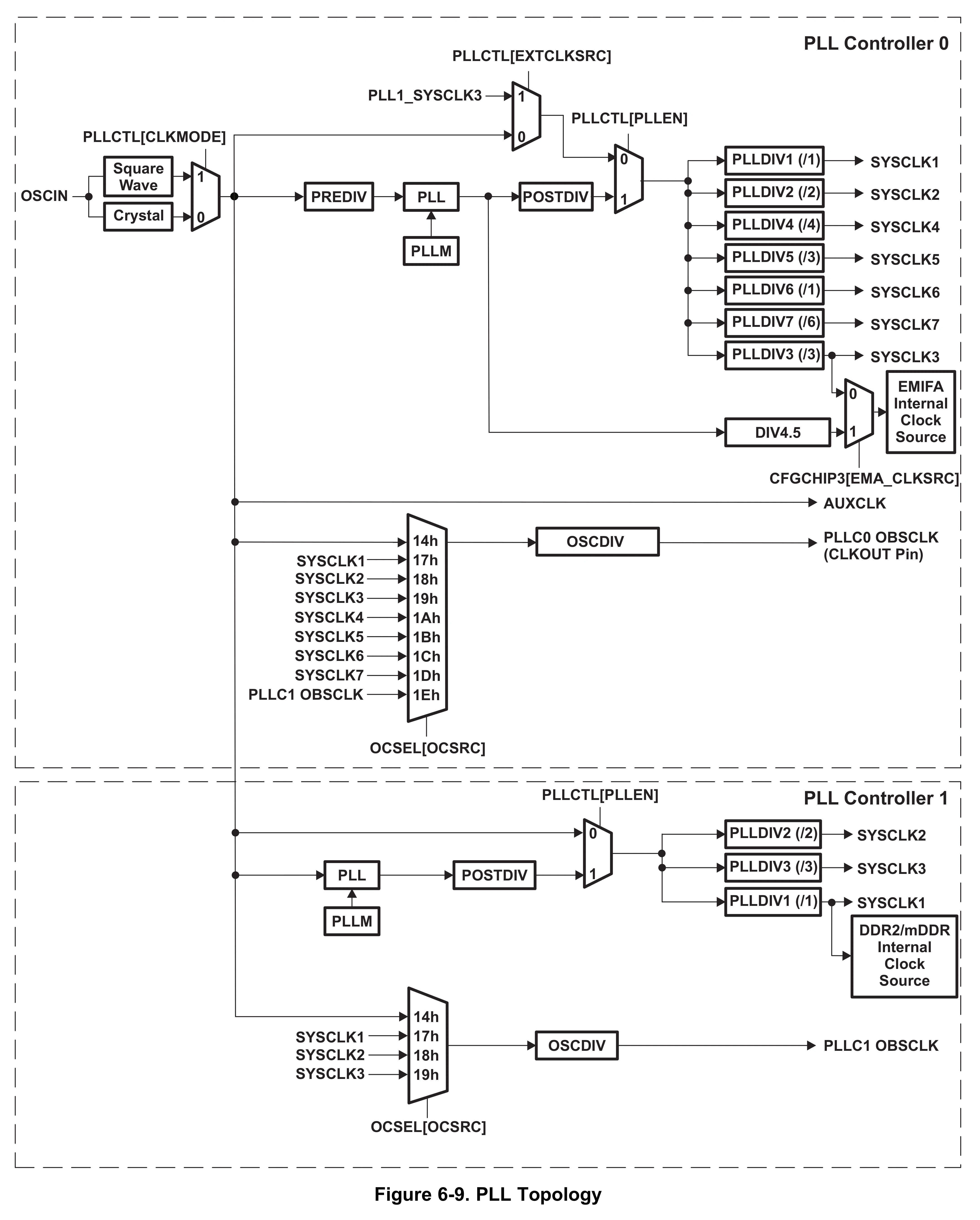

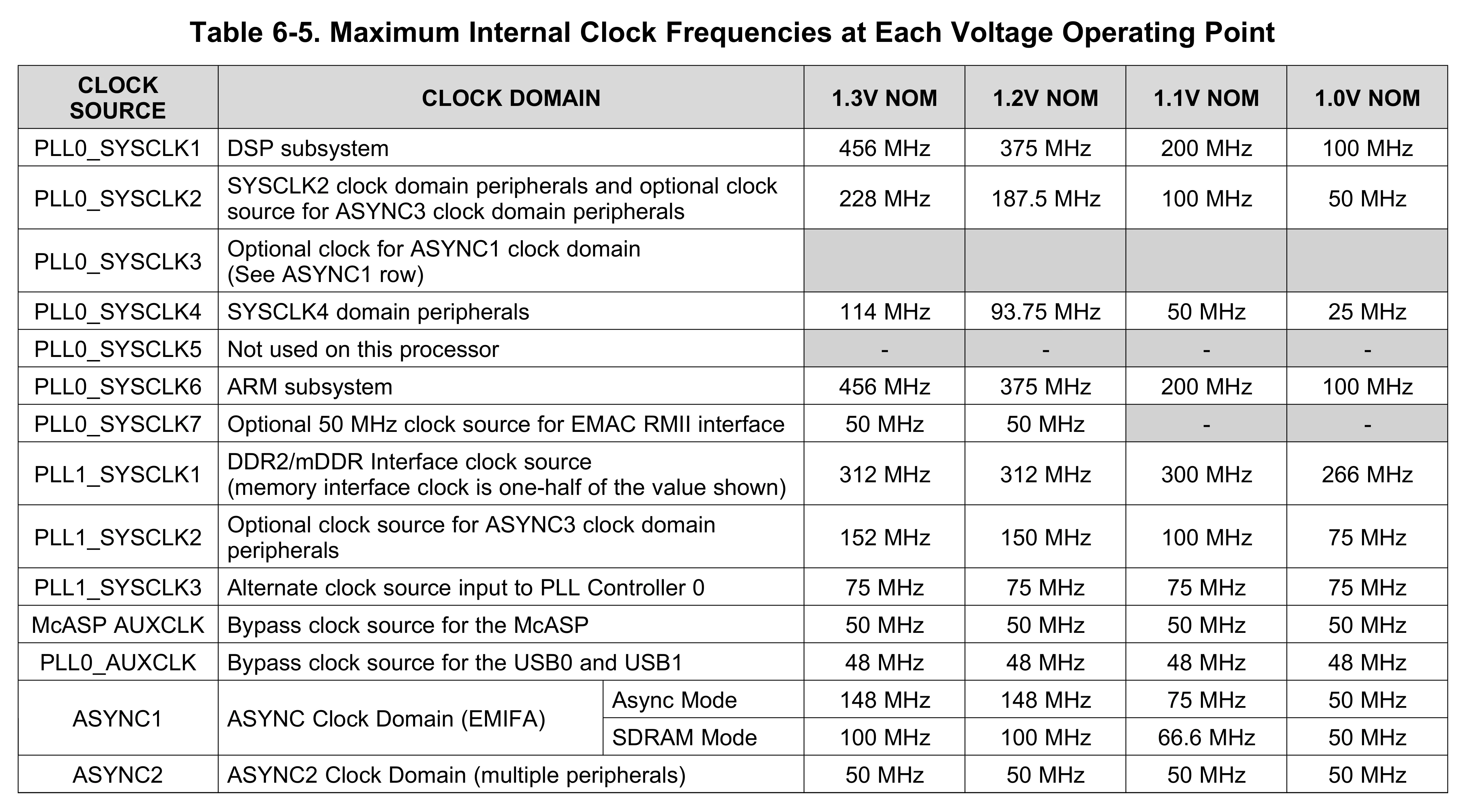

Podsystem zegarowy mikrokontrolera

int davinci_set_sysclk_rate(struct clk *clk, unsigned long rate)

{

unsigned v;

struct pll_data *pll;

unsigned long input;

unsigned ratio = 0;

/* If this is the PLL base clock, wrong function to call */

if (clk->pll_data)

return -EINVAL;

/* There must be a parent... */

if (WARN_ON(!clk->parent))

return -EINVAL;

/* ... the parent must be a PLL... */

if (WARN_ON(!clk->parent->pll_data))

return -EINVAL;

/* ... and this clock must have a divider. */

if (WARN_ON(!clk->div_reg))

return -EINVAL;

pll = clk->parent->pll_data;

input = clk->parent->rate;

/* If pre-PLL, source clock is before the multiplier and divider(s) */

if (clk->flags & PRE_PLL)

input = pll->input_rate;

if (input > rate) {

/*

* Can afford to provide an output little higher than requested

* only if maximum rate supported by hardware on this sysclk

* is known.

*/

if (clk->maxrate) {

ratio = DIV_ROUND_CLOSEST(input, rate);

if (input / ratio > clk->maxrate)

ratio = 0;

}

if (ratio == 0)

ratio = DIV_ROUND_UP(input, rate);

ratio--;

}

if (ratio > pll->div_ratio_mask)

return -EINVAL;

do {

v = __raw_readl(pll->base + PLLSTAT);

} while (v & PLLSTAT_GOSTAT);

v = __raw_readl(pll->base + clk->div_reg);

v &= ~pll->div_ratio_mask;

v |= ratio | PLLDIV_EN;

__raw_writel(v, pll->base + clk->div_reg);

v = __raw_readl(pll->base + PLLCMD);

v |= PLLCMD_GOSET;

__raw_writel(v, pll->base + PLLCMD);

do {

v = __raw_readl(pll->base + PLLSTAT);

} while (v & PLLSTAT_GOSTAT);

return 0;

}

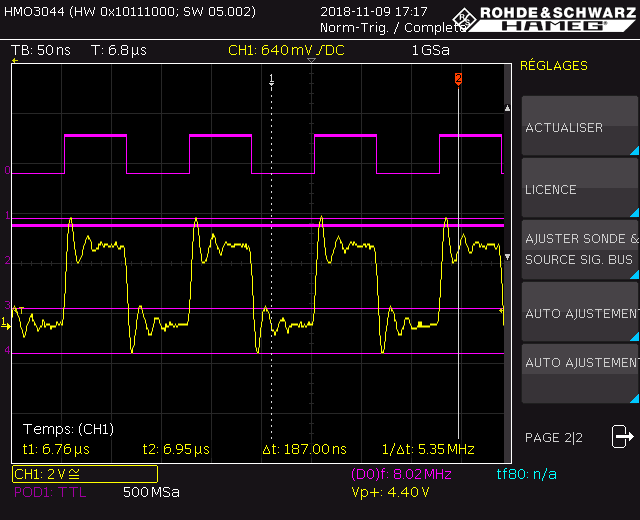

Propagacja zegara w systemie

Długość fali

\(\lambda = \frac{v}{f}\)

\(\lambda = \frac{v}{f} = \frac{3\cdot10^{8}\frac{\text{m}}{\text{s}}}{10\text{GHz}}\)

\(\lambda = \frac{v}{f} = \frac{3\cdot10^{8}\frac{\text{m}}{\text{s}}}{10\text{GHz}} = \frac{3\cdot10^{11}\frac{\text{mm}}{\text{s}}}{10\cdot10^9\frac{1}{\text{s}}}\)

\(\lambda = \frac{v}{f} = \frac{3\cdot10^{8}\frac{\text{m}}{\text{s}}}{10\text{GHz}} = \frac{3\cdot10^{11}\frac{\text{mm}}{\text{s}}}{10\cdot10^9\frac{1}{\text{s}}} = 30\text{mm}\)

Zegary czasu rzeczywistego

Przeznaczenie czasu rzeczywistego

- wyświetlanie czasu użytkownikowi

- logowanie zdarzeń

- wykonywanie zaplanowanych zadań

- komunikacja z innymi urządzeniami (np. TDMA)

- licencjonowanie funkcjonalności

Dostarczenie czasu rzeczywistego

- liczenie czasu w programie

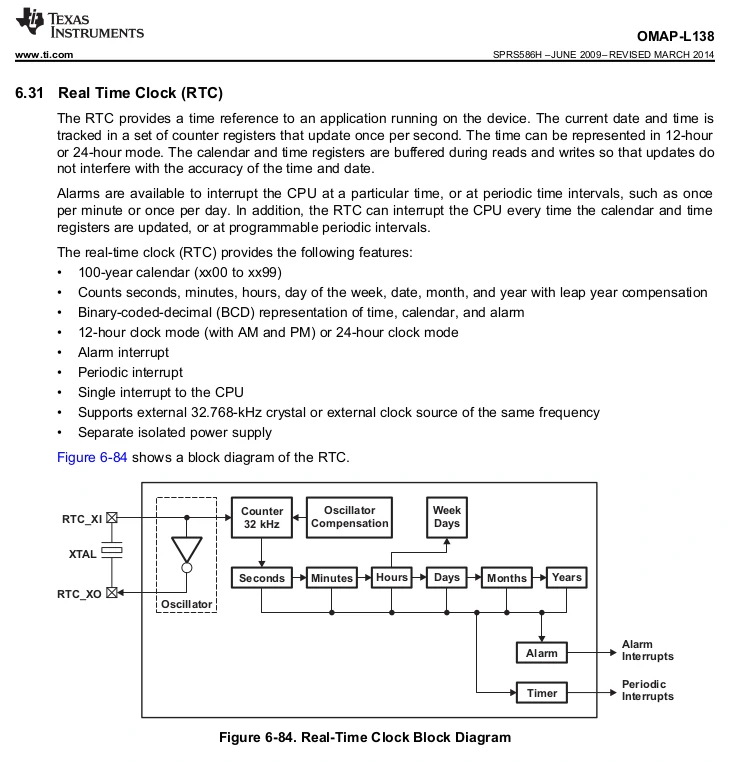

- RTC zintegrowany w mikrokontrolerze

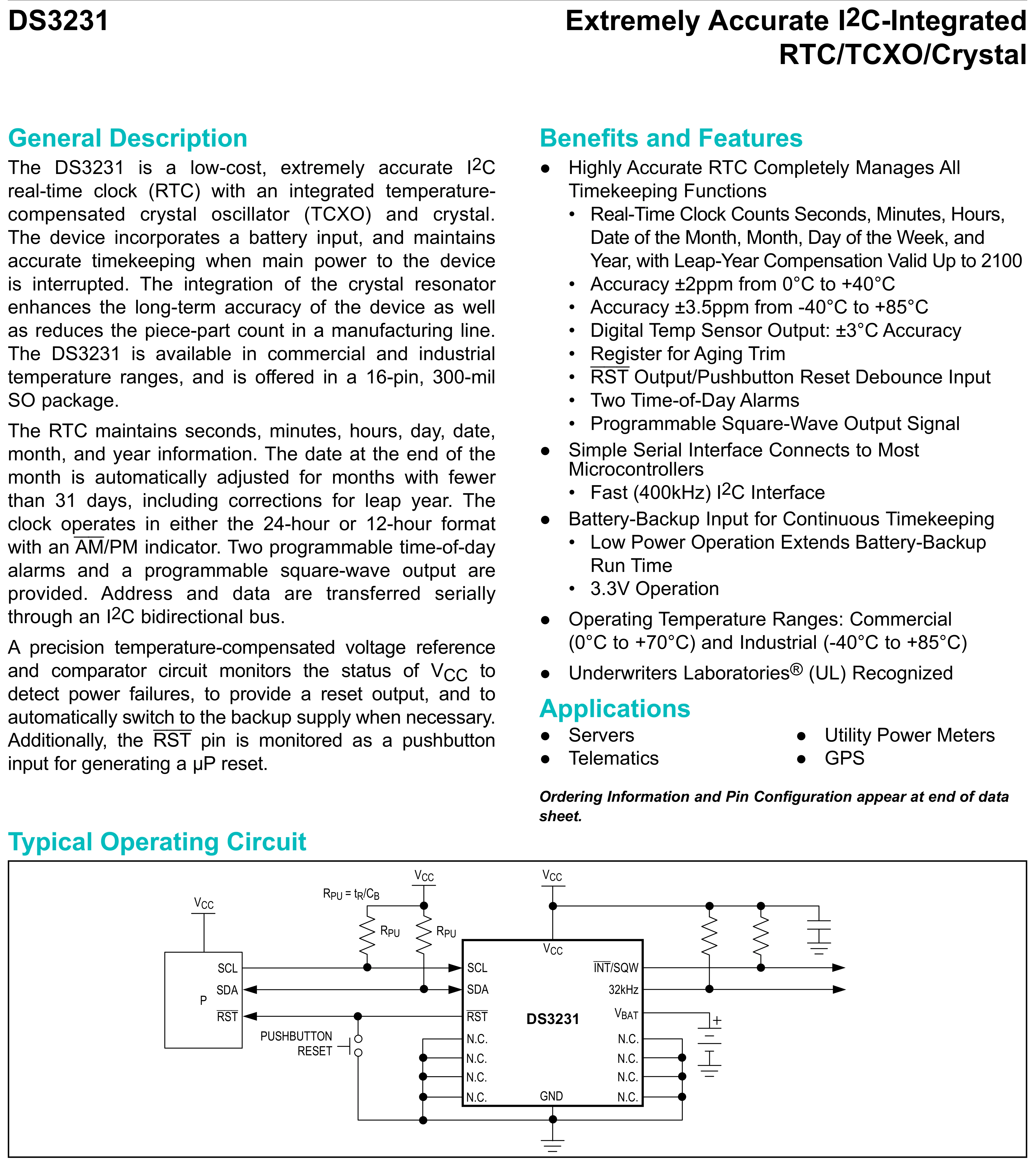

- RTC zewnętrzny

- odbiornik GNSS (np. GPS)

- NTP (Network Time Protocol)

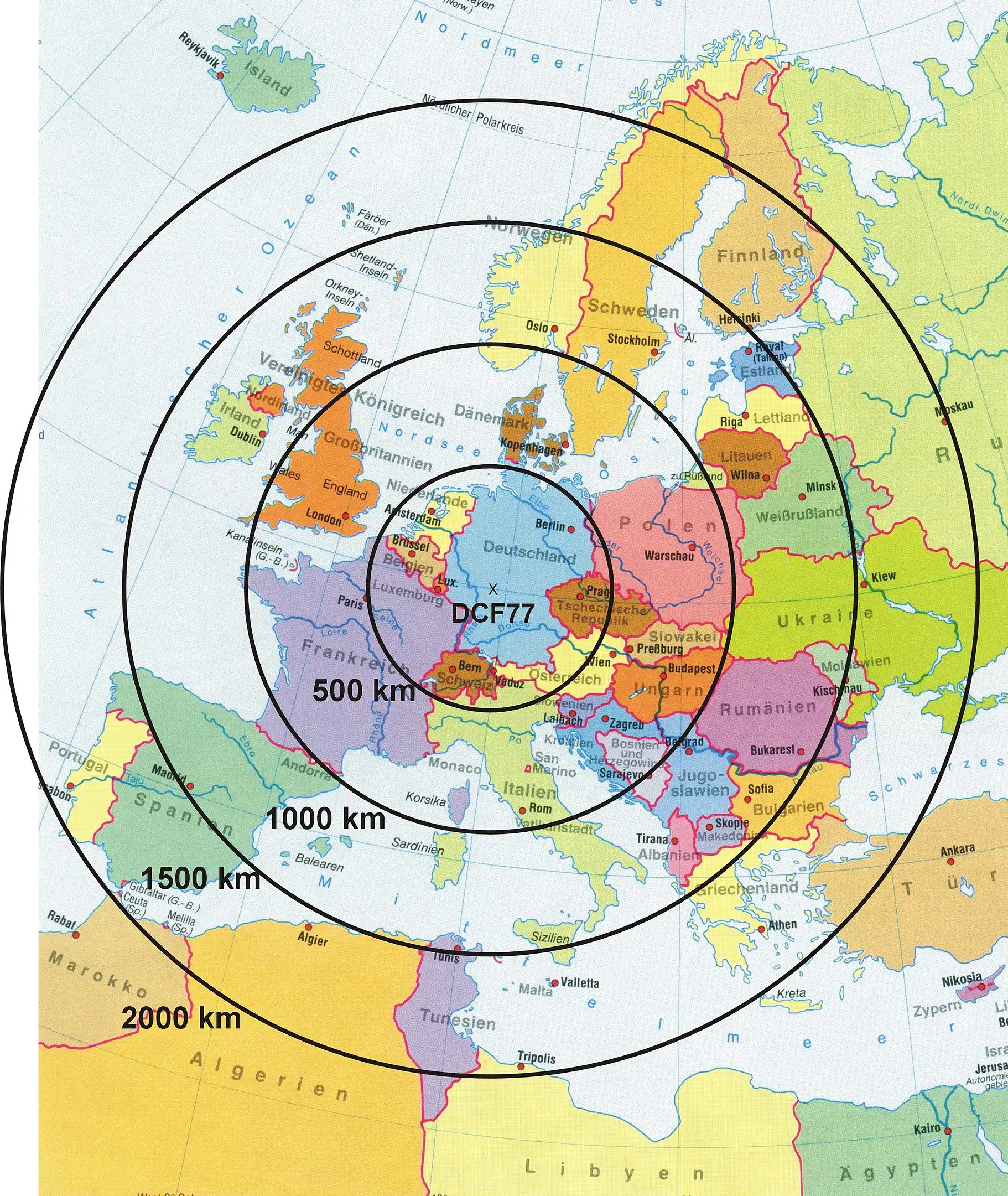

- DCF77 (50kW@77,5kHz — 2000km)

- GSM

- RDS (Radio Data System) — ±100ms

- Bluetooth (sparowany telefon komórkowy)

Częstotliwość oscylatora

Dlaczego \(f = 32{,}768\text{kHz}\)?

\(t = \frac{32{,}768\text{kHz}}{2^{n}}\)

\(t = \frac{32{,}768\text{kHz}}{2^{15}}\)

\(t = \frac{32{,}768\text{kHz}}{2^{15}} = 1\text{s}\)