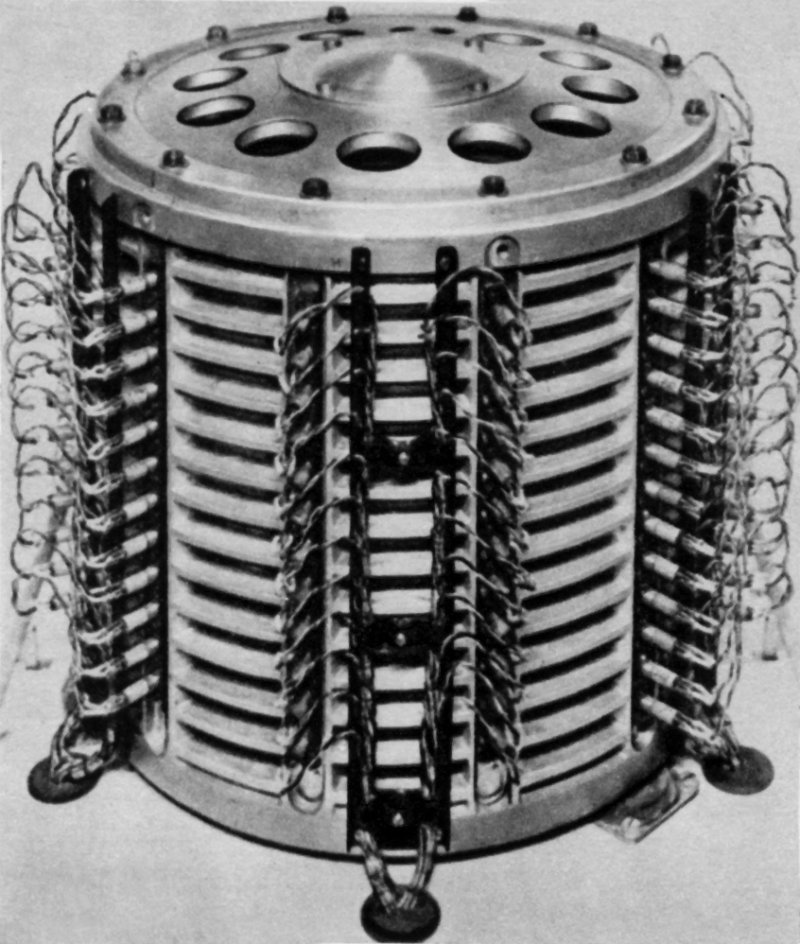

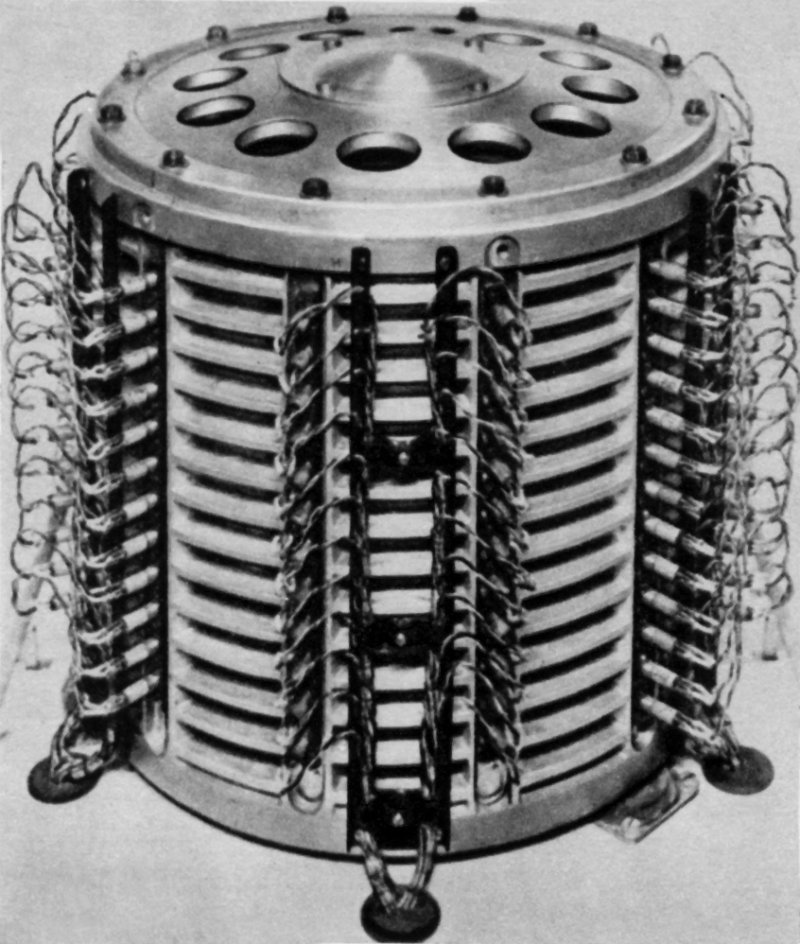

Pamięć bębnowa B-3

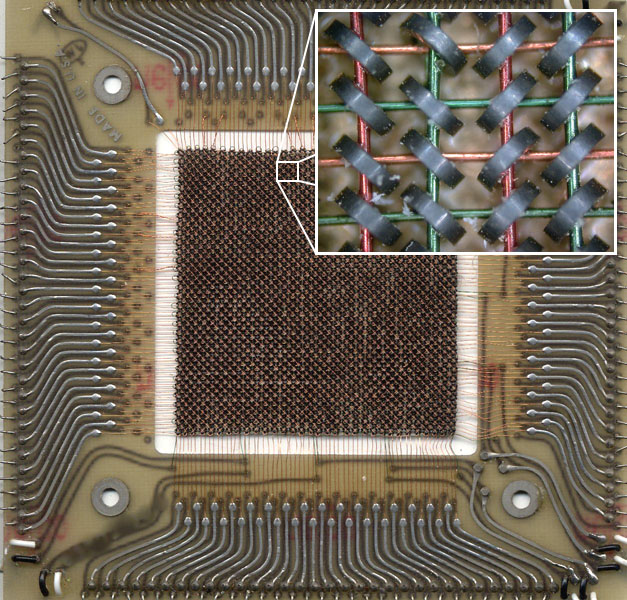

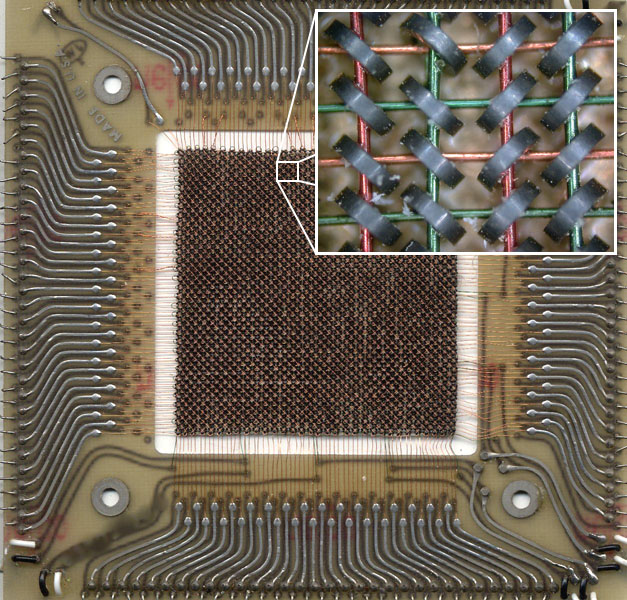

Pamięć ferrytowa

Pamięci operacyjne

(RAM — Random-Access Memory)

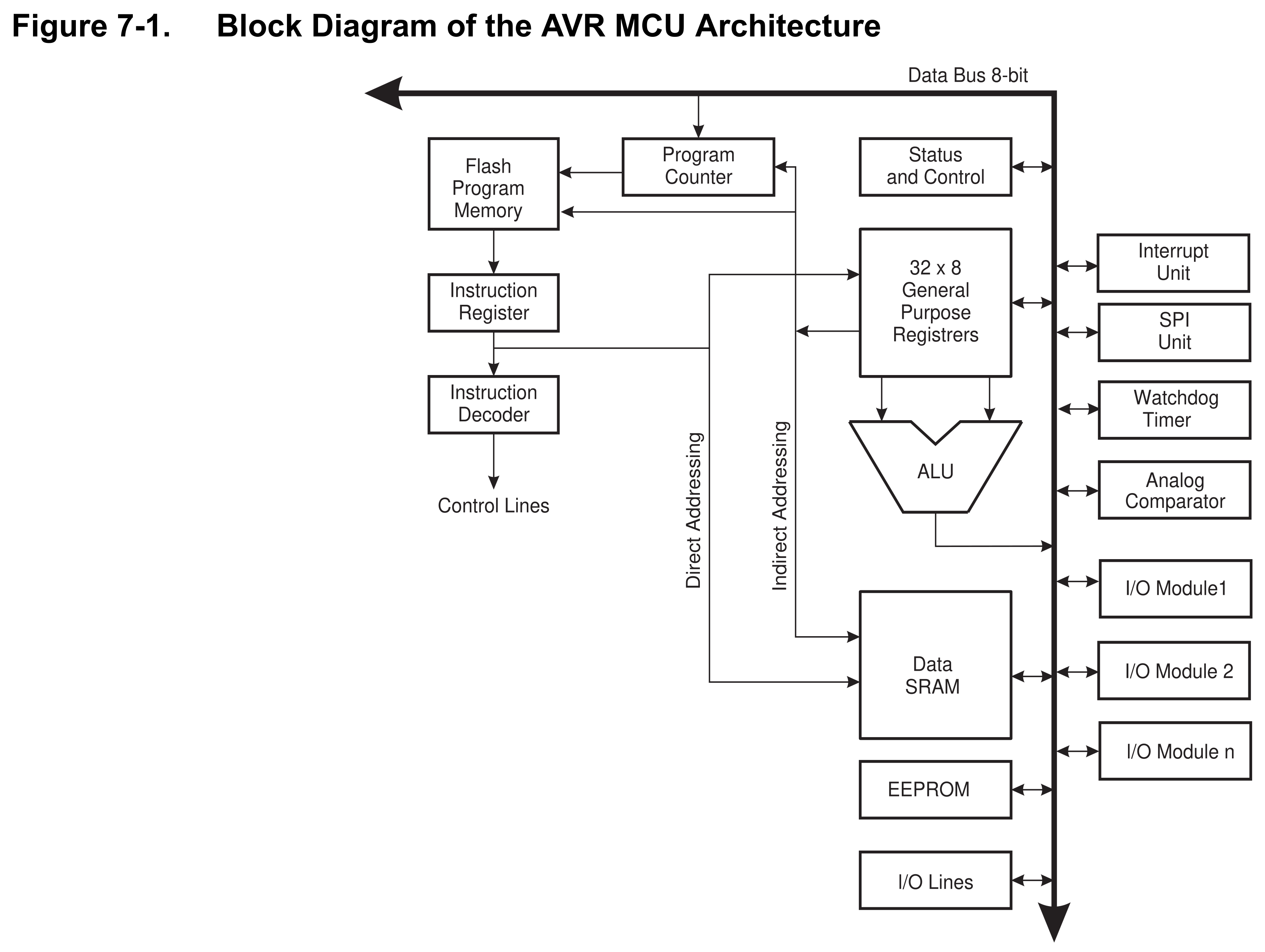

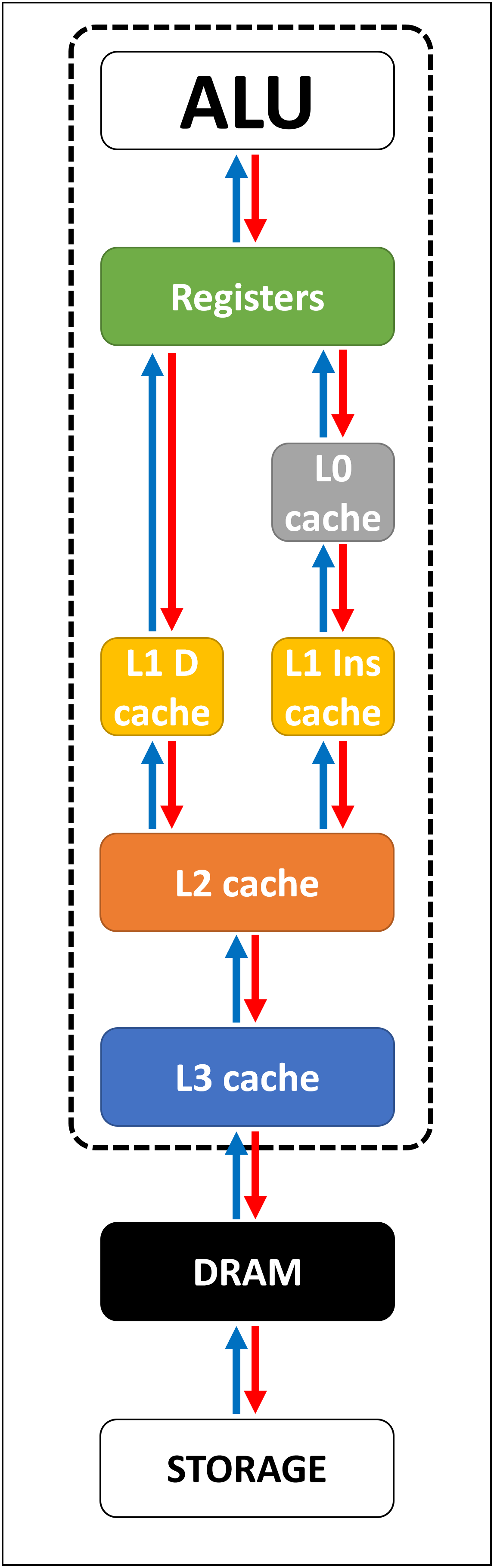

Rejestry procesora

-

najszybsza dostępna pamięć

-

bardzo mały rozmiar (na ogół 8…128 rejestrówpo wielkości 8…64 bitów, czyli 8B…1024B)

-

prostsze procesory pracują tylko na danych w rejestrach

-

praktycznie niedostępne dla programisty w językach wyższego poziomu

-

oprócz rejestrów procesora istnieją również rejestry I/O

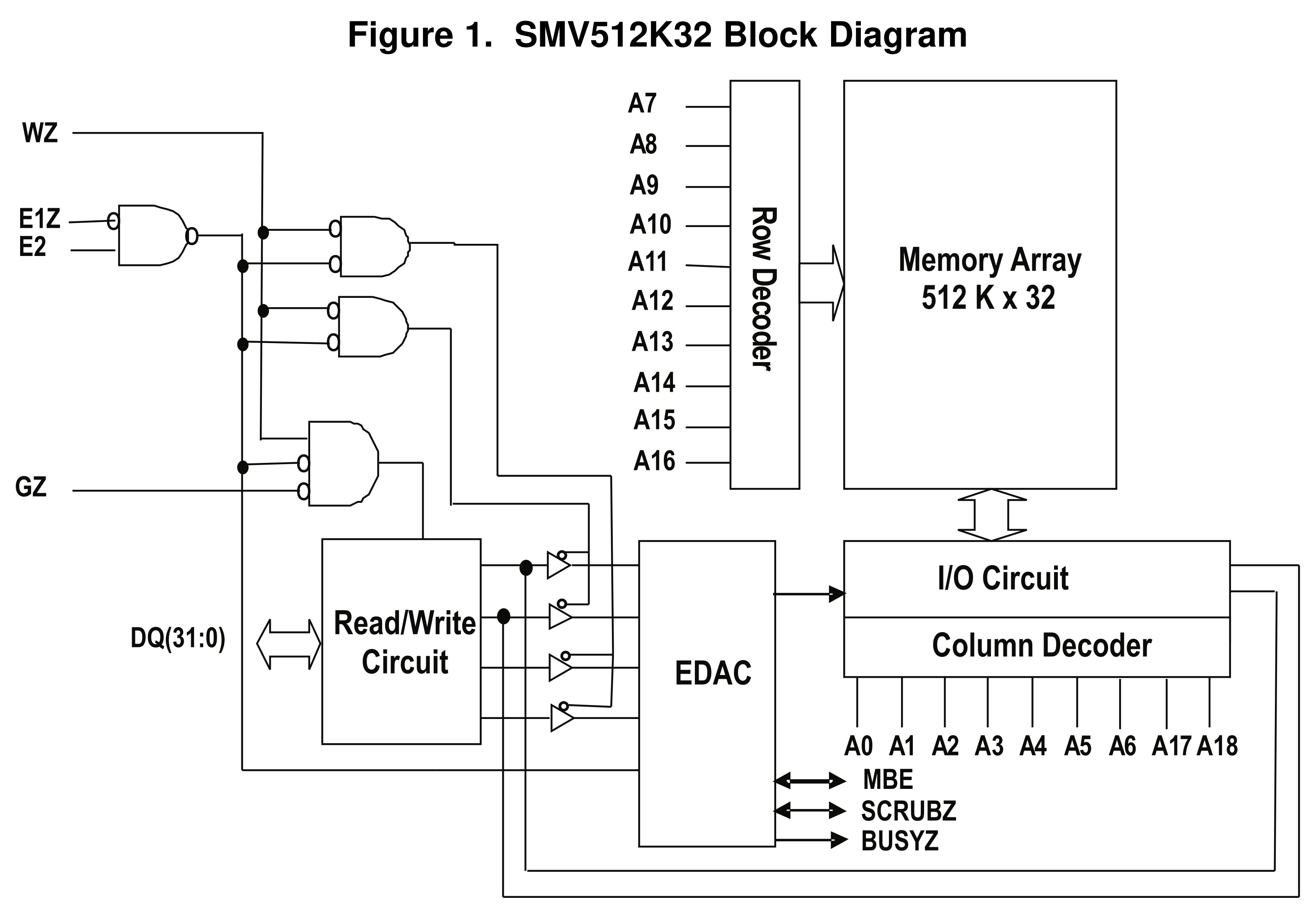

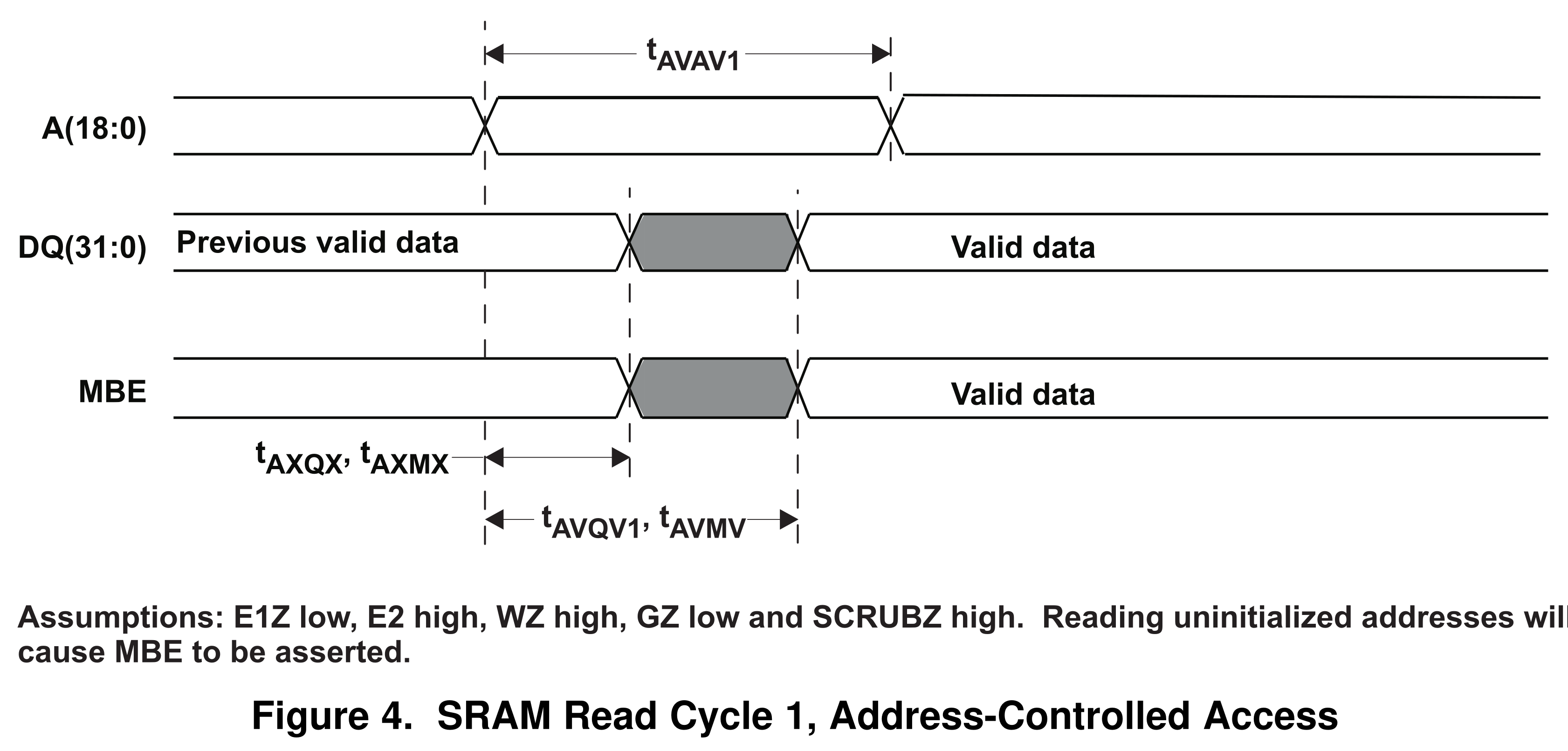

SRAM — Static Random-Access Memory

-

złożona z przerzutników

-

bardzo szybka

-

droga

-

zajmuje dużo miejsca w krzemie

-

zintegrowana w µC

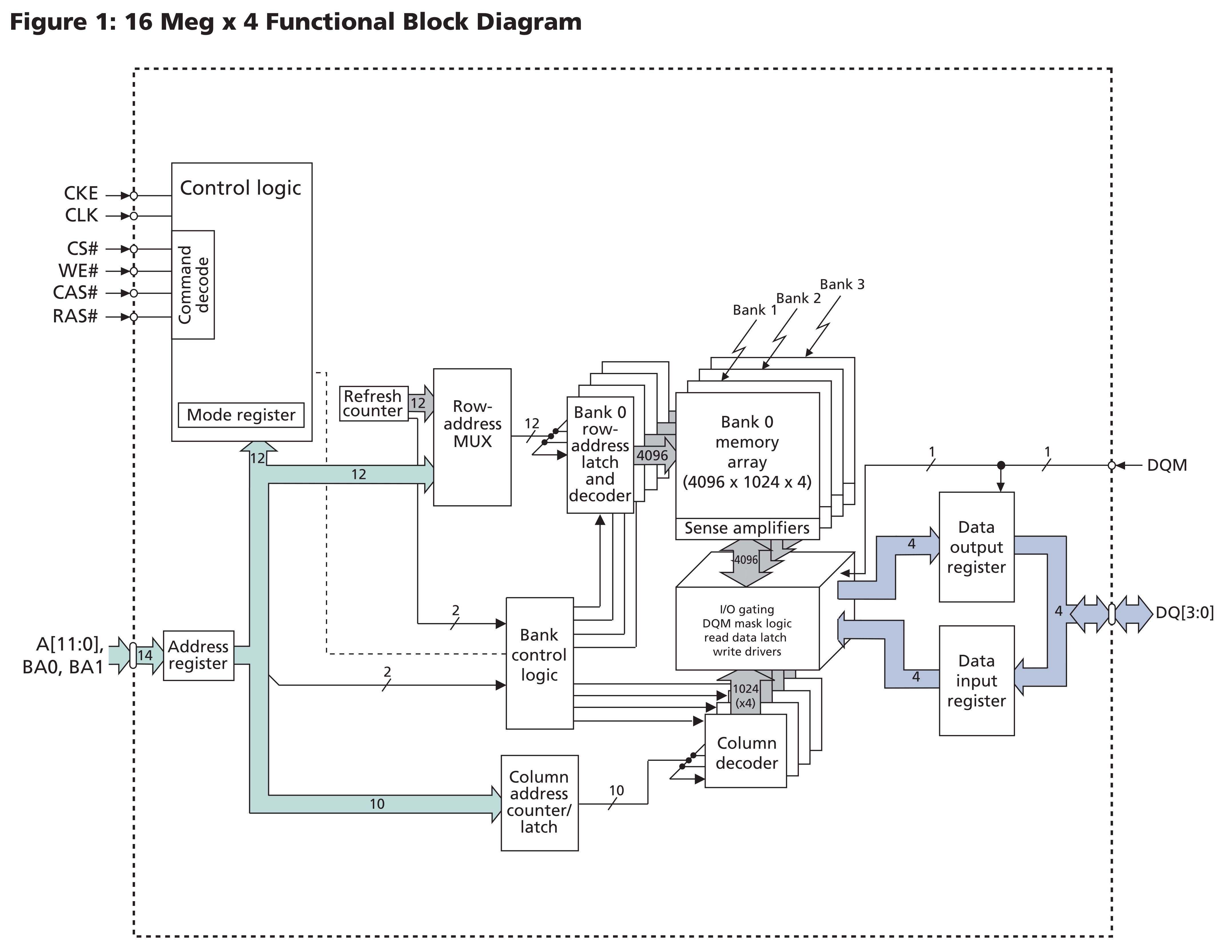

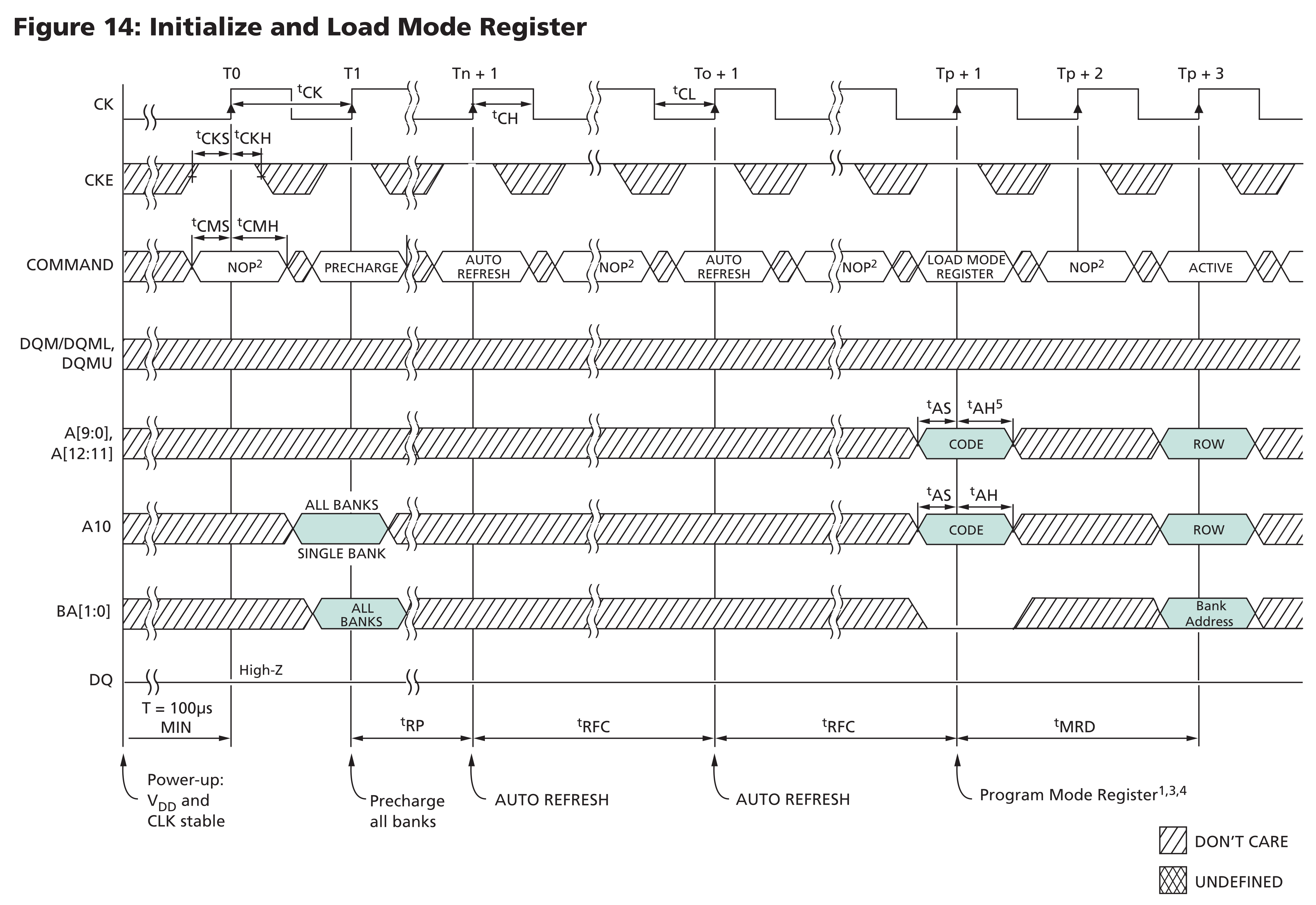

DRAM — Dynamic Random-Access Memory

-

złożona z kondensatorów i tranzystorów

-

wymaga odświeżania

-

szybka

-

tania

-

zajmuje mało miejsca w krzemie

-

układ zewnętrzny

-

skomplikowane optymalizacje (przeplot, potoki)

-

wersja asynchroniczna (starsza) i synchroniczna (SDRAM, DDR SDRAM)

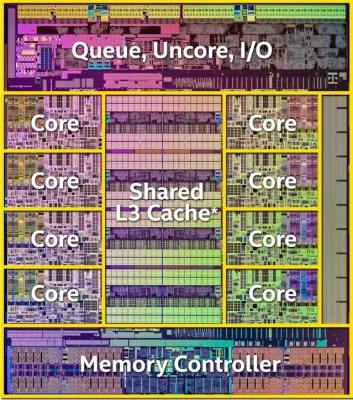

Intel Pentium M

| Pamięć | Cykle |

|---|

| Rejestr | ≤1 |

| L1d | ~3 |

| L2 | ~14 |

| RAM | ~240 |

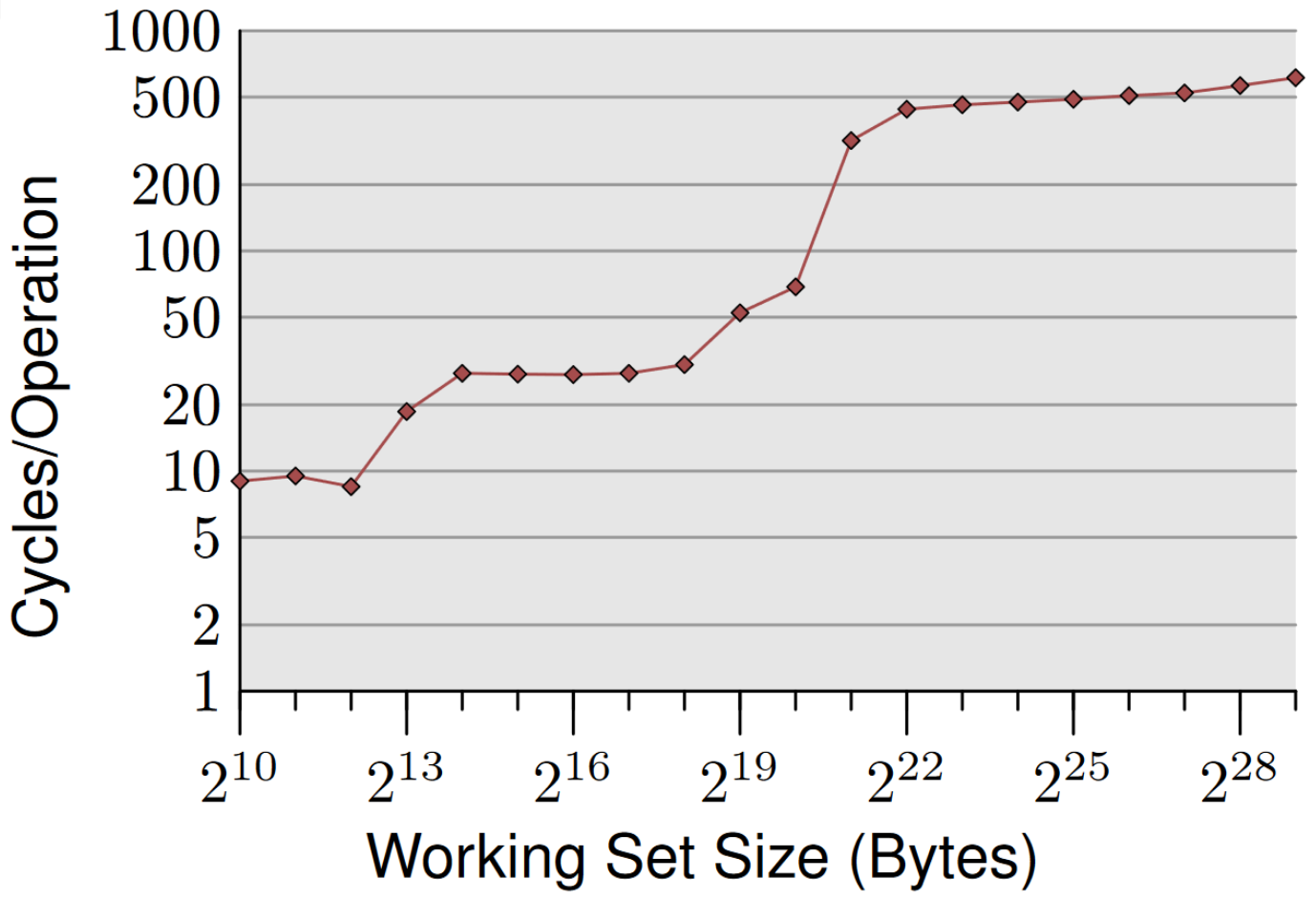

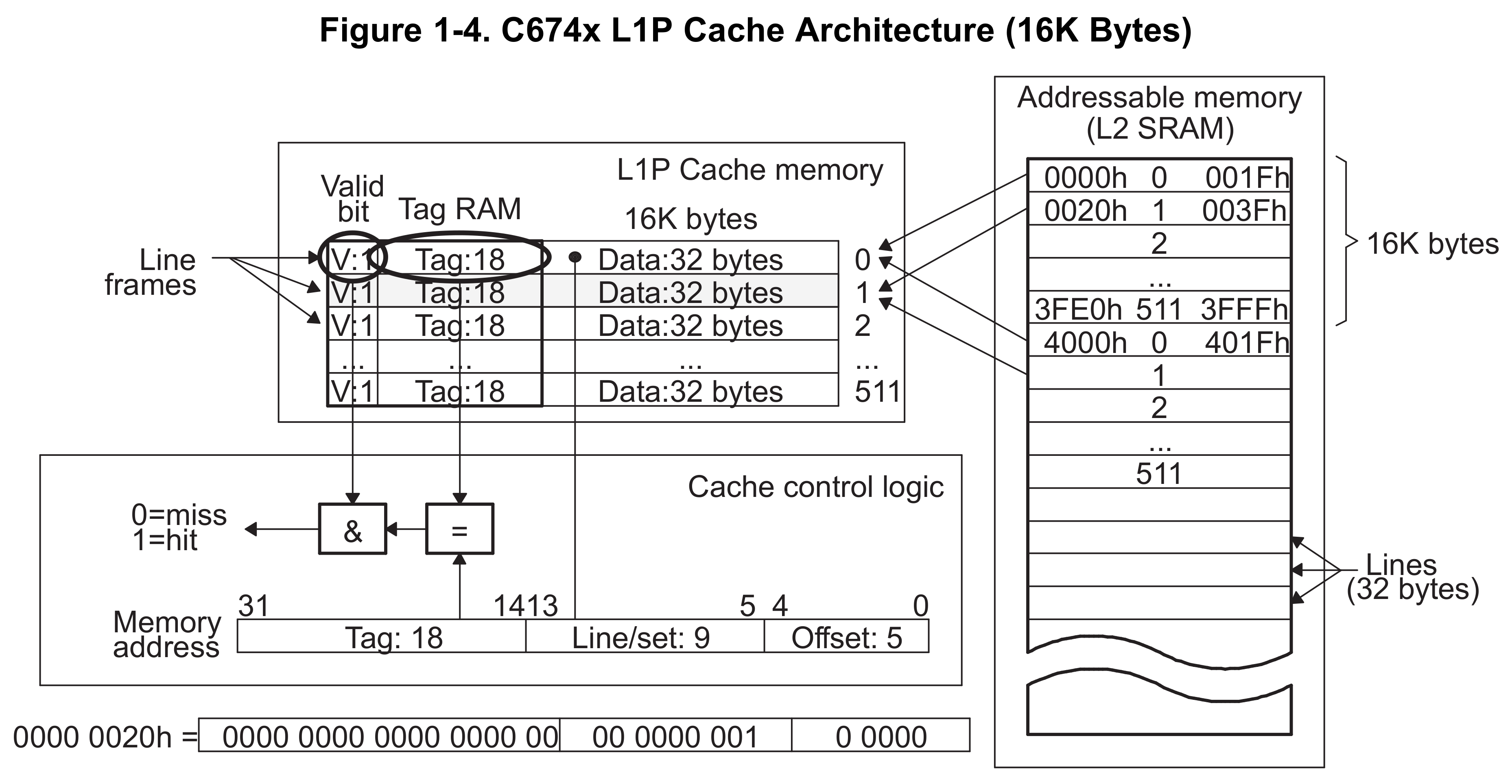

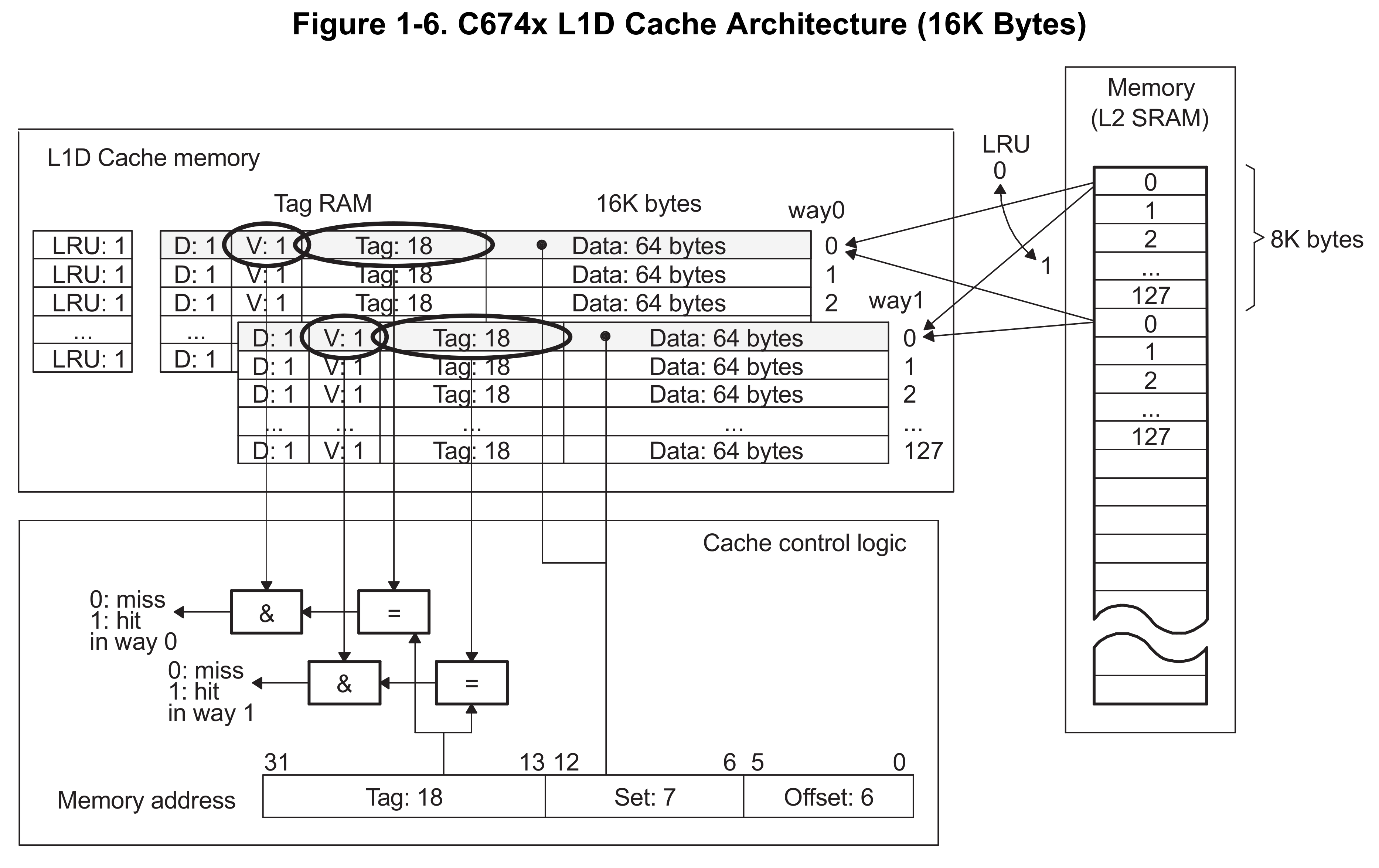

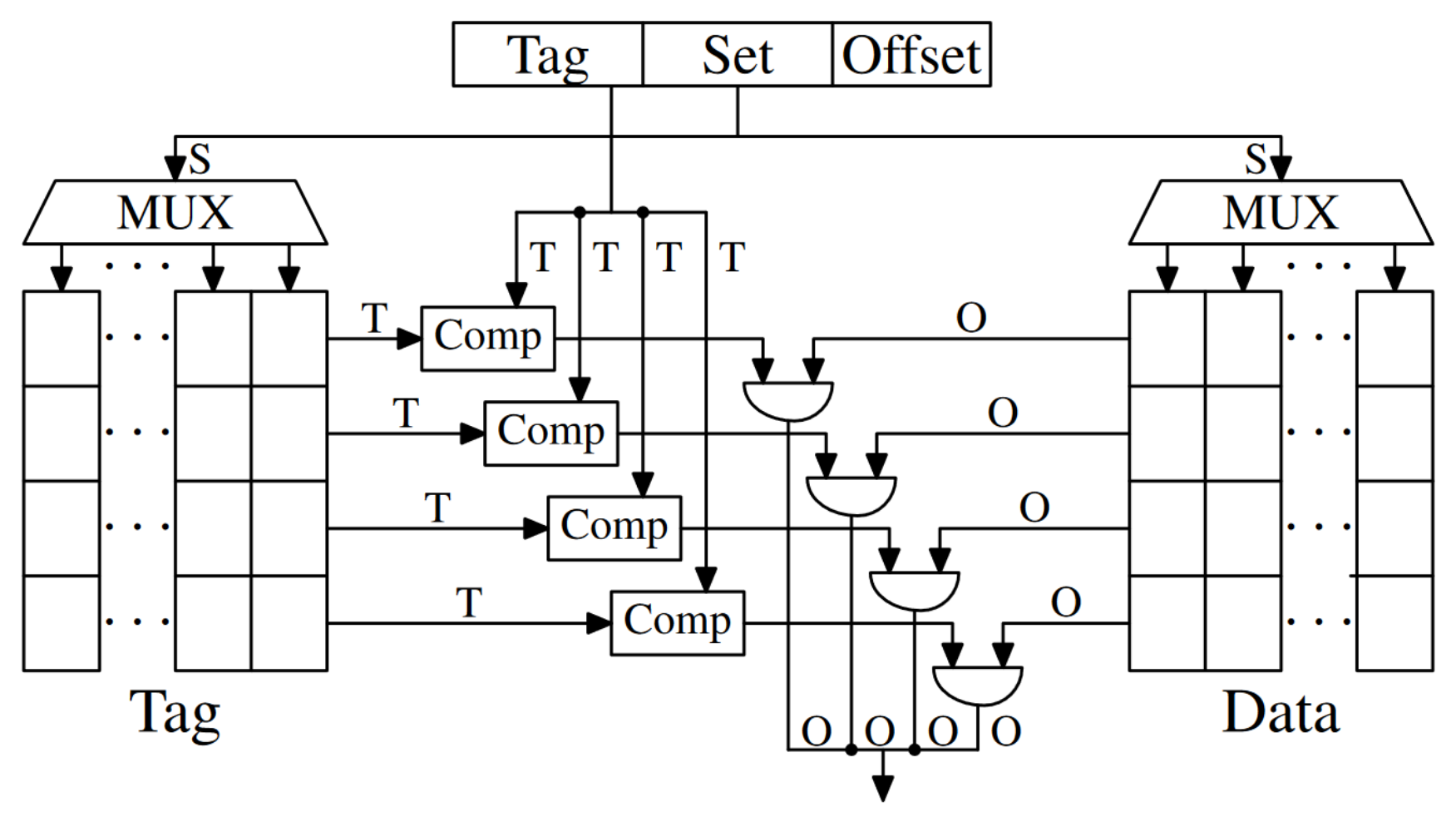

Cache

-

kompromis między granulacją a narzutem na adresowanie linii

-

programista prawie nie ma wpływu na jego działanie

-

kolejne komplikacje w systemach wielordzeniowych

-

ma bardzo duży wpływ na wydajność procesora

DMA — Direct Memory Access

-

umożliwia peryferiałom dostęp do pamięci bez angażowania rdzenia procesora

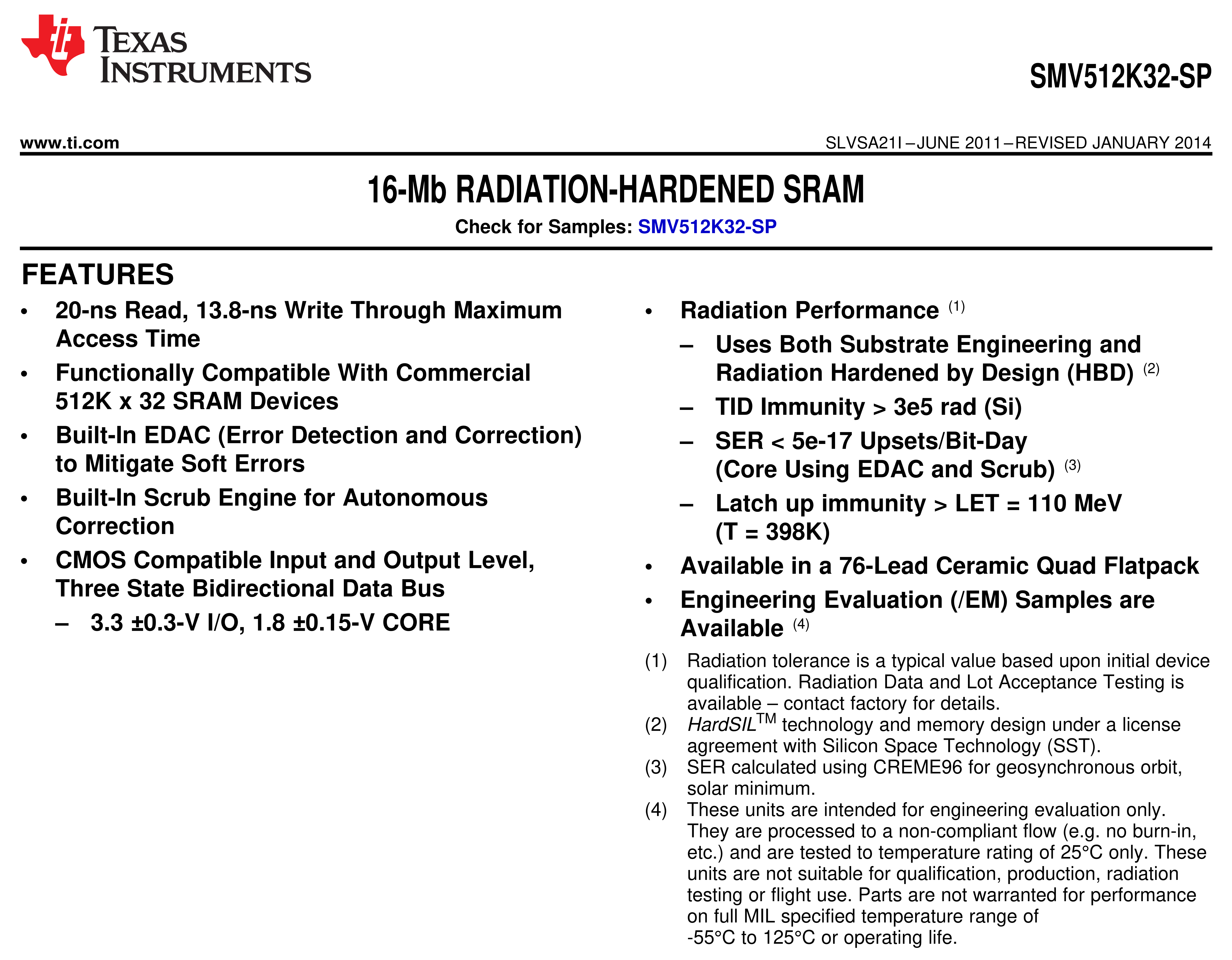

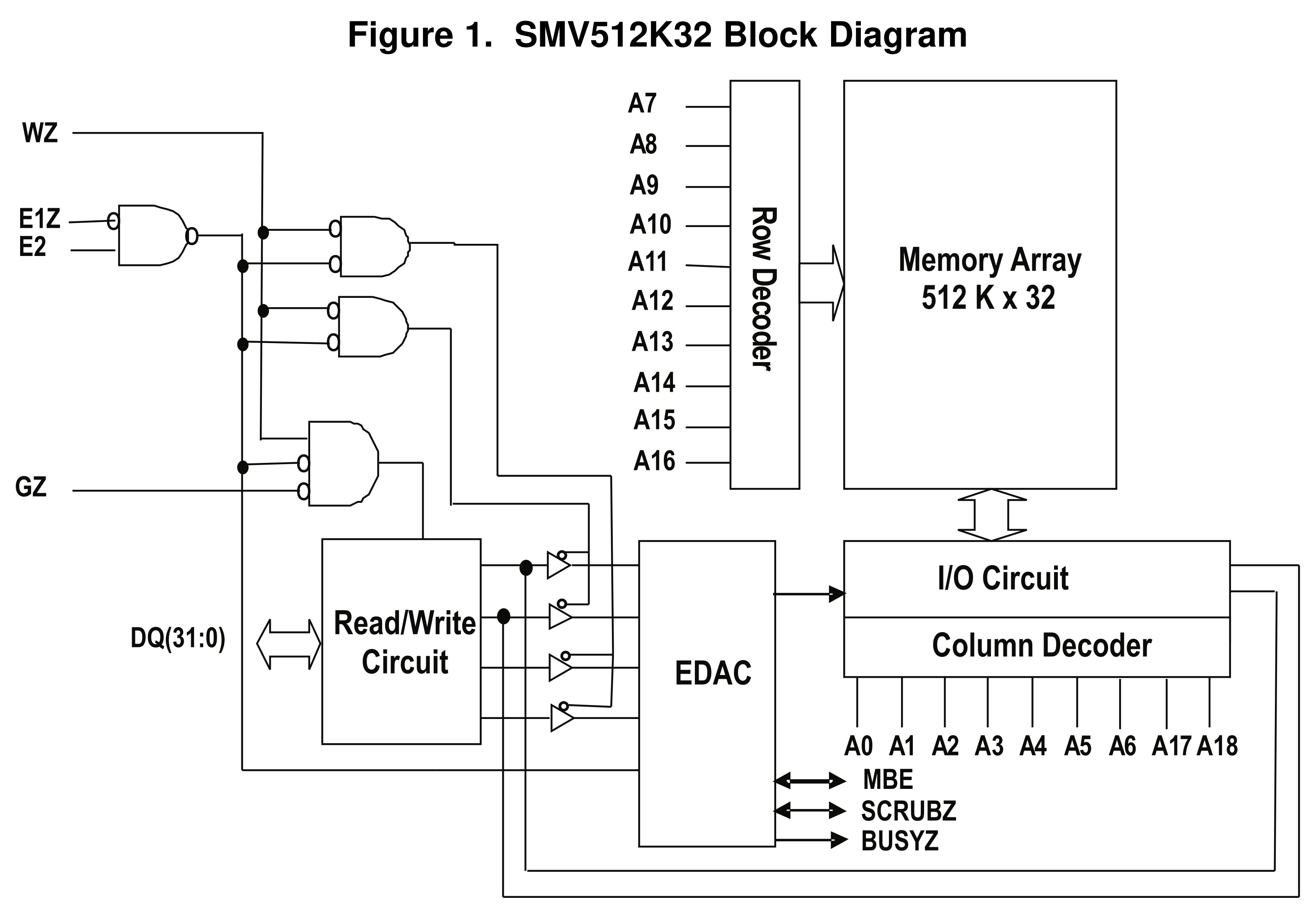

ECC — Error Checking and Correction

-

sonda Cassini–Huygens — 280 błędów dziennie

-

kody nadmiarowe (Hamminga lub Reeda-Solomona)

-

może zmniejszać wydajność pamięci (2%…3%)

-

wymaga wsparcia ze strony procesora

-

stosowane w pamięciach cache procesorów

-

stosowane w serwerach i systemach wbudowanych wysokiej niezawodności

Pamięci masowe (nieulotne)

EPROM — Erasable Programmable Read-Only Memory

-

technologia historyczna

-

programowana wysokim napięciem >20V

-

kasowana promieniowaniem UV

EEPROM — Electrically Erasable Programmable Read-Only Memory

-

programowana i kasowana elektrycznie

-

zazwyczaj niewielka pojemność

-

małe erase blocks (1 B)

-

duża liczba cykli R/W (>100 000)

-

stosowana w µC jako pamięć danych

-

stosowana w kartach kredytowych, SIM, kluczach

-

dostępna jako oddzielne US na I2C, SPI, 1-Wire

Flash

-

rozwinięcie technologii EEPROM

-

może osiągać ogromne pojemności (vide SSD)

-

duże erase blocks (rzędu KiB)

-

często mniejsza liczba cykli R/W (np. 10 000)

-

stosowana w µC jako pamięć programu

-

stosowana w pendrive'ach, kartach pamięci, SSD

-

dostępna jako oddzielne US na SPI, QSPI, równoległy

NOR Flash vs NAND Flash

| NOR | NAND |

|---|

| Pojemność | <256MiB | >256MiB |

| Cena/bit | większa | mniejsza |

| R swobodny | szybki | wolny |

| R/W sekwencyjny | wolny | szybki |

| Bit flipping | śladowy | istotny |

| Bad blocks | 0% | do 2% |

| Retencja | 20 lat | 10 lat |

| Przeznaczenie | program | dane |

Obsługa wad pamięci NAND Flash

-

sprzętowo — FTL (Flash Translation Layer)

-

programowo — UBIFS (Unsorted Block Image File System)

-

bad blocks

-

wear leveling

-

memory scrubbing (obsługa bit flipping)

-

write back cache

-

ECC (CRC)

Inne pamięci nieulotne

-

BBRAM (Battery-Backed RAM)

-

FRAM (Ferroelectric RAM)