Wykład 7:

Magistsrale komunikacyjne

Mariusz Chilmon

m.chilmon@amw.gdynia.pl

uc.vmario.org

Magistrale równoległe vs. szeregowe

Właściwości magistral równoległych

- naturalne dla procesora

- szybsze od szeregowych (przy tym samym taktowaniu)

- wymagają wiele linii (miedź kosztuje!)

- przy szybkich zegarach na długich liniach zniekształcają sygnał

Właściwości magistral szeregowych

- wymagają peryferiałów tłumaczących je na magistrale równoległe

- wolniejsze od równoległych (przy tym samym taktowaniu)

- wymagają niewiele linii

- możliwe jest stosowanie szybkich zegarów na długich liniach

SerDes (Serializer/Deserializer)

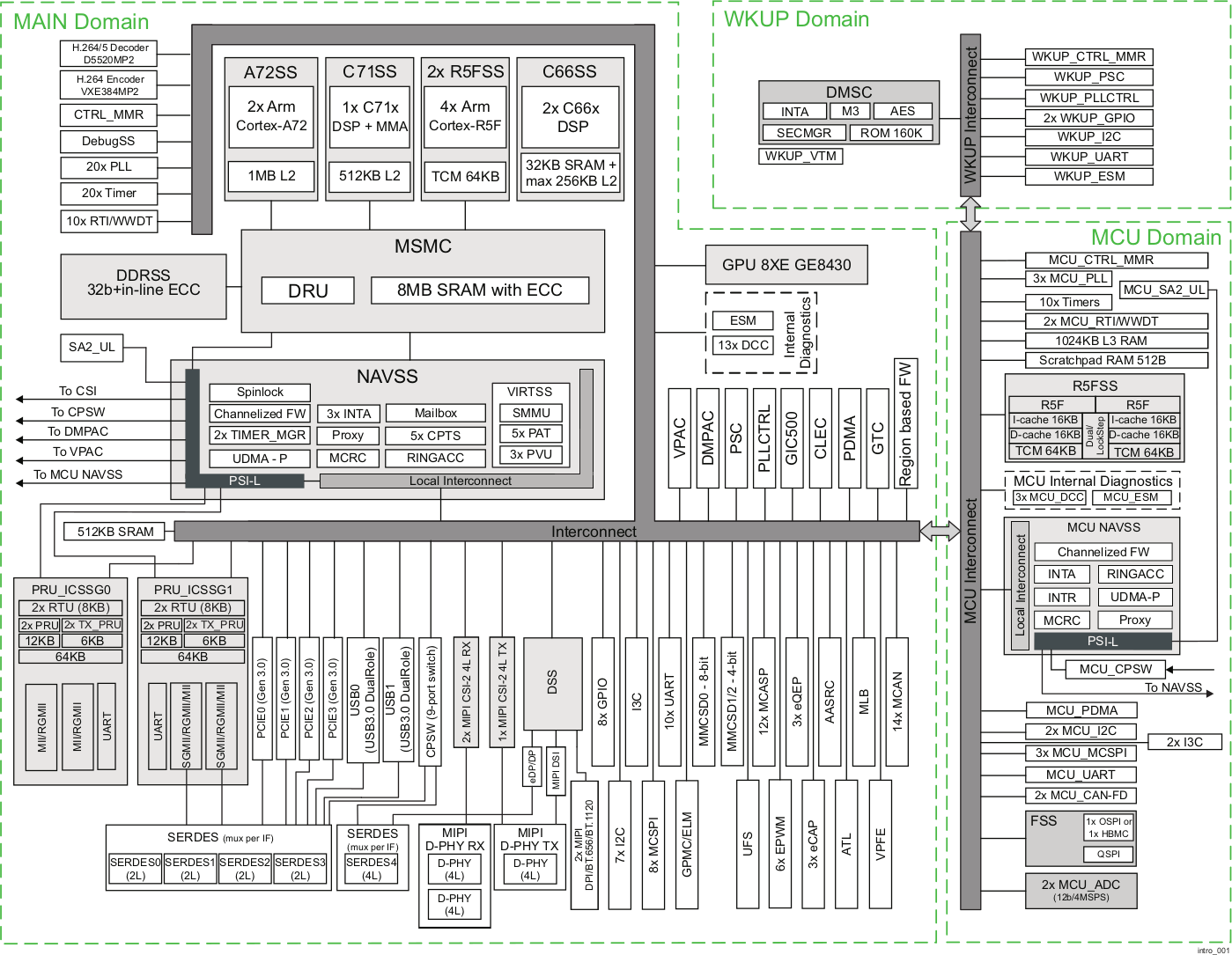

SerDes w J721E

Ewolucja magistral

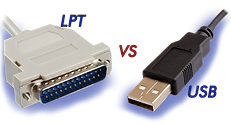

LPT → USB

Ewolucja magistral

ATA → SATA

Ewolucja magistral

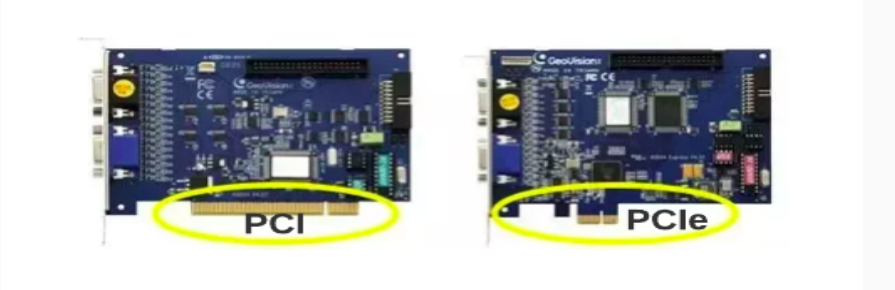

PCI → PCI-E x1, x2, x4, x8, x16

Magistrale równoległe

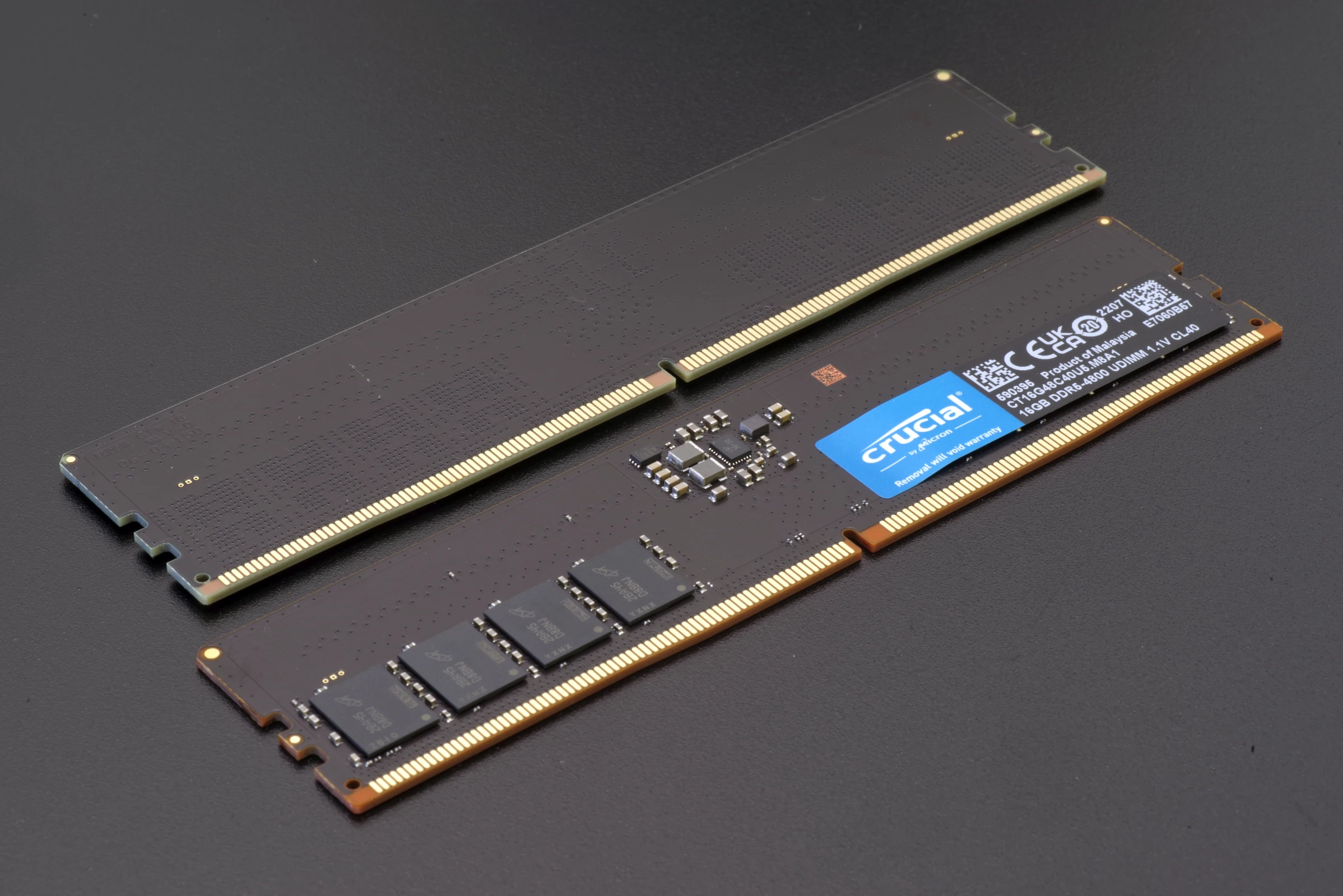

Interfejsy pamięci RAM

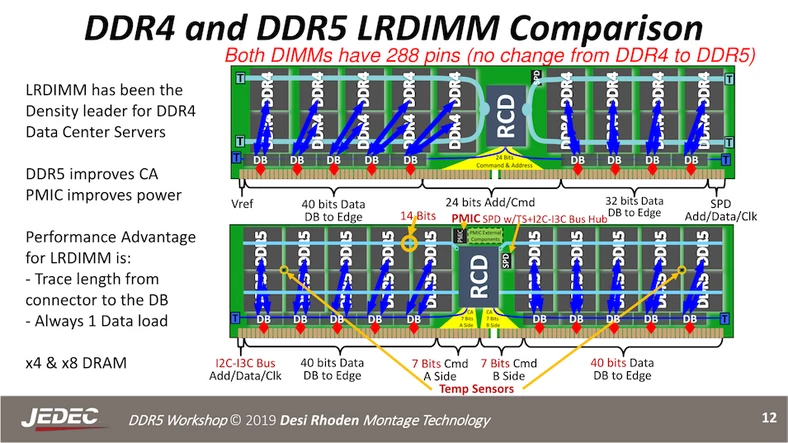

DDR SDRAM 5 (Double Data Rate Synchronous Dynamic Random-Access Memory 5)

- zegar do 3,2 GHz z aktywnymi dwoma zboczami

- dwie szyny danych po 32 bity

\(B = 3{,}2\cdot10^9\text{Hz}\cdot2\cdot32\text{b}\cdot2\)

\(B = 3{,}2\cdot10^9\text{Hz}\cdot2\cdot32\text{b}\cdot2 = 409{,}6\text{Gb/s}\)

Magistrale równoległe w systemach wbudowanych

- pamięci RAM

- pamięci flash

- MII (Media-Independent Interface) (4-bitowy)

- LCD

Magistrale szeregowe

Konfiguracja peryferiałów w µC

- taktowanie

- polaryzacja

- długość słowa

- sposób obsługi buforów

- przerwania i współpraca z DMA

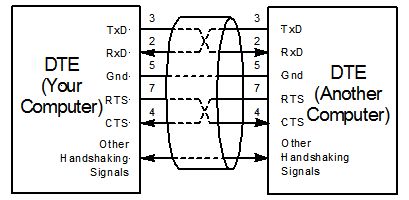

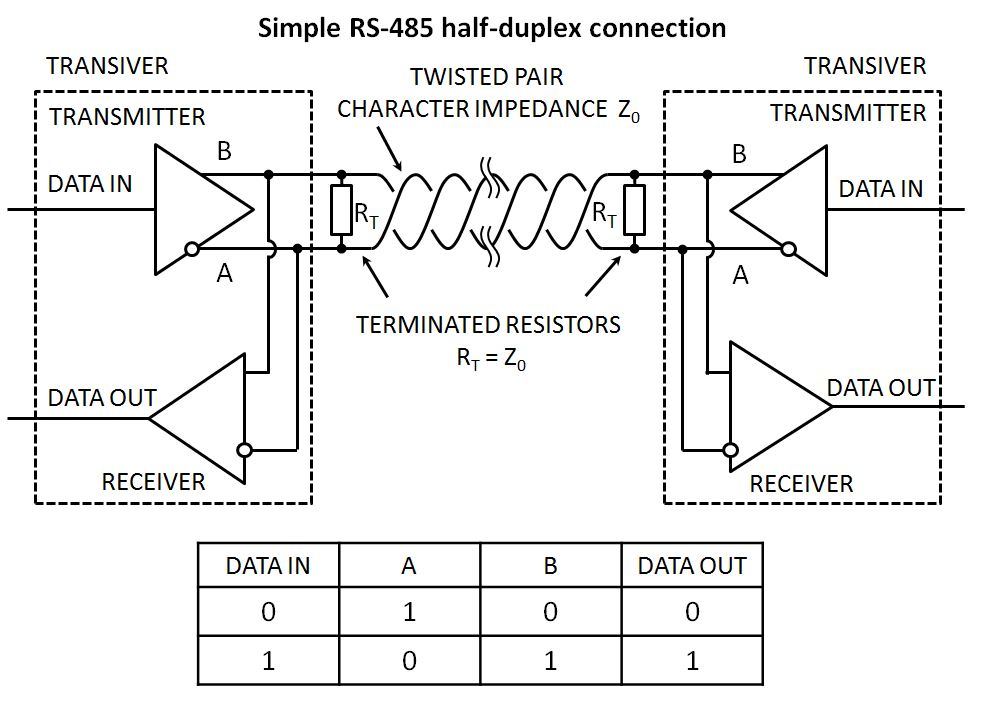

RS-232

- powstał ok. 60 lat temu

- redukowalny do bardzo prostej magistrali point-to-point

- rozszerzalny do szyny z wielodostępem

- wciąż spotykany w PC

- wykorzystywany w automatyce (np. Modbus na RS-485)

- bardzo dobre konwertery na USB (FT232, Moxa)

- wymaga zegara o dokładności <1%

- w µC obsługiwany przez USART (Universal Synchronous and Asynchronous serial Receiver and Transmitter)

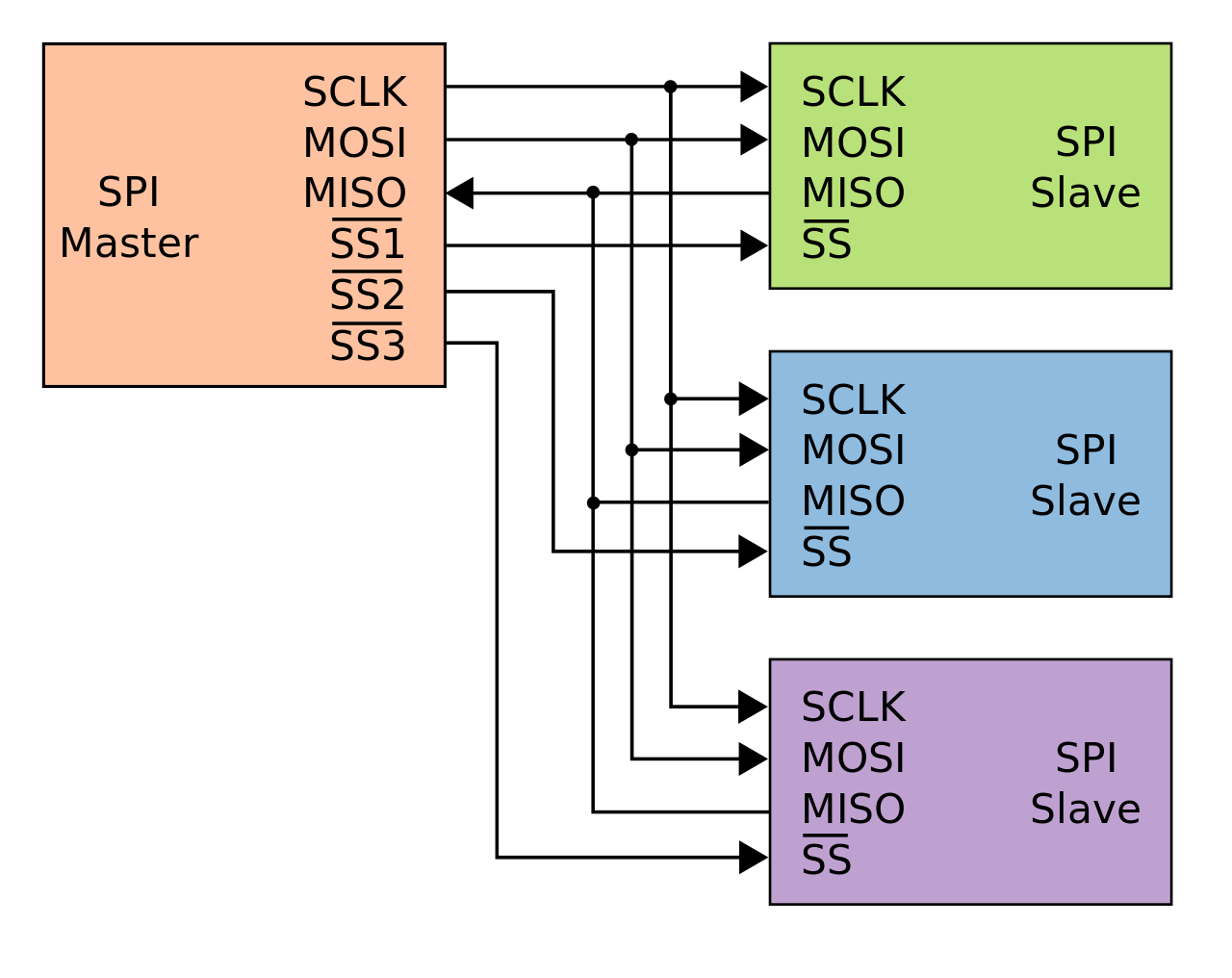

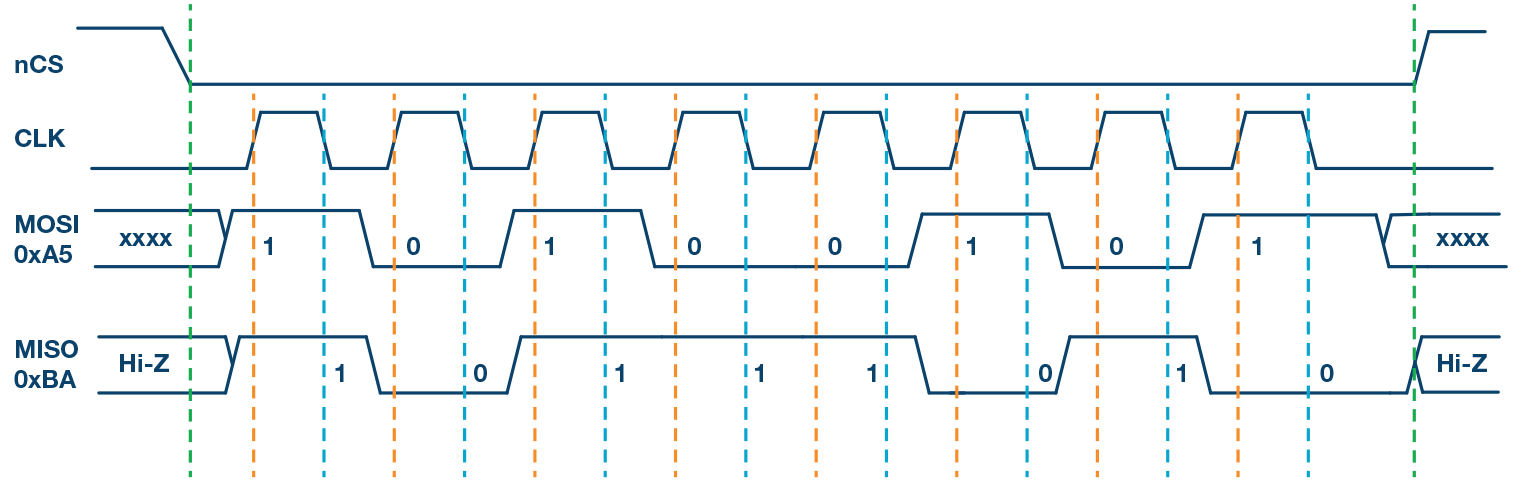

SPI

- Serial Peripheral Interface

- używany do komunikacji między układami scalonymi

- umożliwia wielodostęp, ale wymaga dodatkowych linii

- posiada linię zegarową

- prosty i przewidywalny

- komunikacja zawsze zachodzi w dwie strony jednocześnie

- architektura master-slave

SPI na sterydach

- wersje równoległe: DSPI, QSPI, OSPI

- wersje DDR

- tuningowanie za pomocą linii DQS

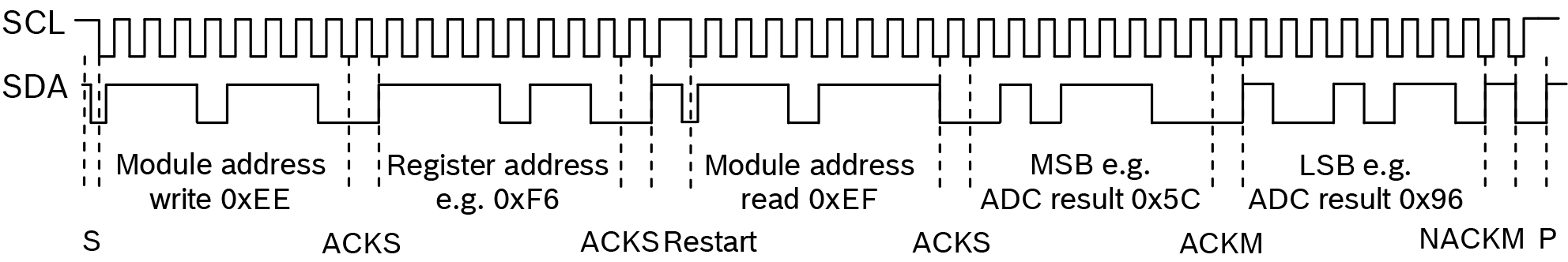

I2C

- Inter-Integrated Circuit

- używany do komunikacji między układami scalonymi

- umożliwia wielodostęp

- wykorzystuje tylko dwie linie + GND

- architektura master-slave

1-Wire

- często używany do komunikacji z czujnikami

- wykorzystuje tylko jedną linię + GND

- umożliwa przesyłanie zasilania linią komunikacyjną

- architektura master-slave

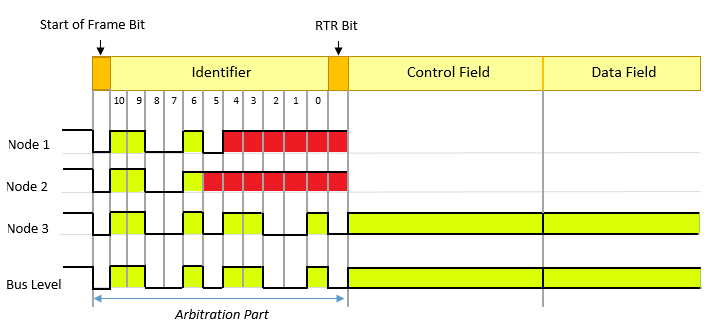

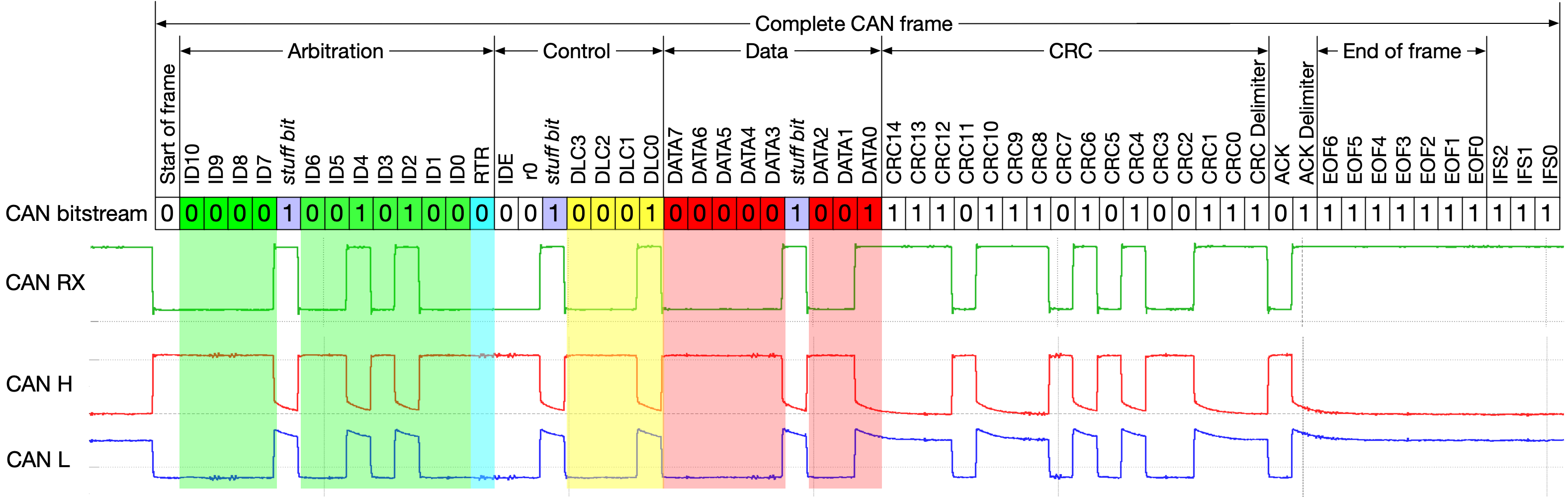

CAN i LIN

- stosowane w motoryzacji

- jedna linia różnicowa

- sprzętowy arbitraż

HDMI

- High-Definition Multimedia Interface

- TMDS (Transition-Minimized Differential Signaling)

- CEC (Consumer Electronics Control)

- ARC (Audio Return Channel)

- HEC (HDMI Ethernet Channel)

- do 42Gbps (HDMI2.1)

Kody

- kody liniowe (8b/10b)

- CRC (Cyclic Redundancy Check)

-

kody korekcyjne:

- kody Hamminga, w szczególności wersja SECDED (Single Error Correction, Double Error Detection)

- kody splotowe

- kody Reeda-Solomona (CD, DVD, Blu-ray)

- przeploty

- funkcje hashujące⁕

- funkcje hashujące bezpiecznie kryptograficznie⁕